## CENTRO DE INVESTIGACIÓN Y DE ESTUDIOS AVANZADOS DEL INSTITUTO POLITÉCNICO NACIONAL

#### Unidad Zacatenco

## Departamento de Computación

# XSCALA: Un marco de desarrollo para soportar programación paralela por tareas en sistemas de cómputo híbridos hetrogéneos

#### **TESIS**

Que presenta

M. en C. José Uriel Cabello Sánchez

Para obtener el grado de

Doctor en Ciencias en Computación

Directores de la Tesis:

Dr. José Guadalupe Rodríguez García Dr. Amilcar Meneses Viveros

## CENTRO DE INVESTIGACIÓN Y DE ESTUDIOS AVANZADOS DEL INSTITUTO POLITÉCNICO NACIONAL

### Campus Zacatenco

## Department of Computer Science

# XSCALA: A Framework for Supporting Parallel Task Programming on Hybrid Heterogeneous Computing Systems

#### **THESIS**

By

M.Sc. José Uriel Cabello Sánchez

Thesis submitted in fulfillment of the requirements for the degree of

# PhD in Computer Science

Thesis Advisors:

PhD. José Guadalupe Rodríguez García PhD. Amilcar Meneses Viveros

**Mexico City**

### Resumen

# XSCALA: Un marco de desarrollo para soportar programación paralela por tareas en sistemas de cómputo híbridos hetrogéneos

por Uriel Cabello

El avance en la comprensión y la solución de algunos problemas de investigación está estrechamente relacionado con nuestra capacidad de procesar grandes cantidades de datos lo más rápido posible. Por otro lado el uso de clústeres de computadoras de memoria híbrida equipados con aceleradores heterogéneos se ha convertido en la herramienta estándar más rentable para resolver dichos problemas dentro de periodos de tiempo razonables.

Hoy en día cada nodo en un clúster de computadoras está equipado no sólo con los tradicionales CPU, sino con otras unidades de porcesamiento de propósito general como los son las unidades de procesamiento gráfico (Graphic Processing Units ó GPUs) o los coprocesadores que tienen múltiples núcleos conectadas en configuraciones especiales, diseñadas para acelerar la ejecución de tareas simples pero repetitivas.

El enfoque actual para la programación de aplicaciones para sistemas híbridos heterogéneos requiere la combinación de múltiples modelos de programación y una cuidadosa distribución de la carga de trabajo.

Entre los principales problemas encontrados en las aplicaciones desarrolladas con el enfoque actual encontramos:

- Gestión compleja y subutilización de los recursos de cómputo.

- Aplicaciones fuertemente vinculadas a entornos de ejecución específicos.

- Poca abstracción del hardware subyacente.

En esta tesis presentamos XSCALA: Un marco de desarrollo para soportar programación paralela por tareas en sistemas de cómputo híbridos hetrogéneos. Los principales objetivos de XSCALA son dos: Simplificar el diseño y la implementación de aplicaciones aprovechando las ventajas de los sistemas híbridos heterogéneos y asegurar la escalabilidad de las aplicaciones que se están desarrollando.

Nuestro marco está diseñado para permitir la creación y distribución de tareas y está compuesto por una interfaz de programación de aplicaciones (Application Programming

Interface ó API) y un *middleware* que proporciona servicios en tiempo de ejecución como distribución de datos y calendarización.

Con el fin de demostrar las ventajas de nuestra propuesta presentamos la implementación basada en tareas de algunas aplicaciones. Realizamos varios experimentos que varían el tamaño del problema, la técnica de calendarización y el entorno de ejecución sin requerir modificaciones ni recompilación del código fuente programado con XSCALA.

## Abstract

## XSCALA: A Framework for Supporting Parallel Task Programming on Hybrid Heterogeneous Computing Systems

by Uriel Cabello

The advance in the understanding and solution of several research problems is closely related with our ability to processing large amounts of data as fast as possible. On the other hand the use of hybrid memory cluster computers with heterogeneous accelerators has become the standard and most cost-effective tool for solving those problems within reasonable amounts of time.

Nowadays each node in a cluster computer is equipped not only with the traditional CPU, but with other general purpose computing units like graphical processing units (GPUs) or coprocessors having multiple cores wired in special configurations, designed to accelerate the execution of simple but repetitive tasks.

The current approach for programming applications on hybrid heterogeneous systems requires the combination of multiple programming models and a careful distribution of the workload.

Among the major problems found in the applications developed with the current approach we find:

- Complex management and under-utilization of computing resources.

- Applications strongly tied to specific execution environments.

- Poor abstraction of the underlying hardware.

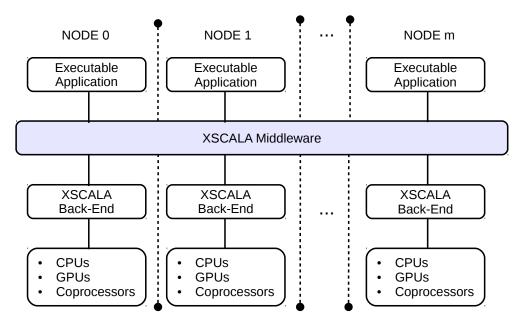

In this thesis we present XSCALA: a framework for supporting parallel task programming on hybrid heterogeneous computing systems. The major objectives of XSCALA are twofold: Simplify the design and the implementation of applications harnessing the advantages of hybrid heterogeneous systems and ensure the scalability of the applications being developed.

Our framework is designed to enable the creation and distribution of task and is composed of an application programming interface and a middleware that provides runtime services like data distribution and scheduling.

In order to demonstrate the advantages of our proposal we present the task-based implementation of some applications. We performed several experiments varying the size of

the problem, the scheduling technique, and the execution environment without requiring neither modifications nor recompilation of the applications code programmed with XSCALA.

# A grade cimientos

A mis asesores por sus valiosas aportaciones.

Al CINVESTAV por las cátedras, la infraestructura y los apoyos otorgados que fueron invaluables en mi formacion.

Al CONACYT por la beca otorgada para la realización de esta tesis.

# Contents

| R            | esum  | en            |                                                         | iii |

|--------------|-------|---------------|---------------------------------------------------------|-----|

| $\mathbf{A}$ | bstra | ıct           |                                                         | v   |

| $\mathbf{A}$ | grade | ecimie        | ntos                                                    | vi  |

| $\mathbf{C}$ | onter | $_{ m nts}$   |                                                         | ix  |

| 1            | Intr  | oducti        | ion                                                     | 1   |

| Ι            | Co    | ntext         |                                                         | 7   |

| 2            | Bac   | kgroui        | $\mathbf{nd}$                                           | 9   |

|              | 2.1   | Basic         | Concepts                                                | 9   |

|              |       | 2.1.1         | Middleware                                              | 9   |

|              |       | 2.1.2         | Frameworks                                              | 10  |

|              |       | 2.1.3         | Portability                                             | 11  |

|              |       | 2.1.4         | Scalability                                             | 11  |

|              | 2.2   | Parall        | el Computer Memory Architectures                        |     |

|              |       | 2.2.1         | Shared Memory Architectures                             |     |

|              |       | 2.2.2         | Distributed Memory Architectures                        |     |

|              |       | 2.2.3         | Hybrid Memory Architectures                             |     |

|              | 2.3   |               | ogeneous Computing Architectures: GPUs and Coprocessors |     |

|              | 2.4   |               | el Programming Models                                   |     |

|              |       | 2.4.1         | Shared Memory Programming Models                        |     |

|              |       | 2.4.2         | Distributed Memory Programming Models                   |     |

|              | 2.5   | 2.4.3         | Hybrid Memory Programming Model                         |     |

|              | 2.5   | 2.5.1         | Parallel Task Programming Model                         |     |

|              |       | 2.5.1 $2.5.2$ | Representation of Workflows with Graphs                 |     |

|              | 2.6   |               | uling                                                   |     |

|              | 2.0   | 2.6.1         | Classification of Scheduling Algorithms                 |     |

|              |       | 2.6.2         | Scheduling Subject to Constraints                       |     |

|              | 2.7   |               | rmance Indicators                                       |     |

| 3            | The   | State         | of the Art                                              | 31  |

|              | 3.1   | Exten         | sions to OpenCL                                         | 31  |

Contents

|    | 3.2 | Extensions to MPI                                                               |      |  |  |

|----|-----|---------------------------------------------------------------------------------|------|--|--|

|    | 3.3 | 1                                                                               |      |  |  |

|    | 3.4 | Frameworks                                                                      |      |  |  |

|    | 3.5 | Summary                                                                         | . 39 |  |  |

| II | Co  | ntributions                                                                     | 41   |  |  |

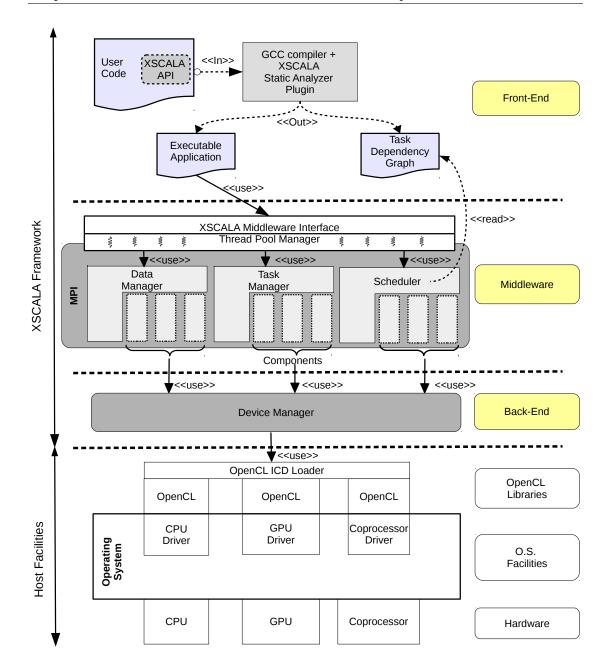

| 4  | The | XSCALA Framework: Architecture and Operation                                    | 43   |  |  |

|    | 4.1 | XSCALA Framework                                                                | . 43 |  |  |

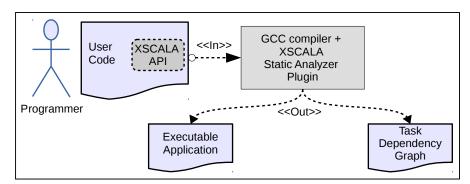

|    |     | 4.1.1 Front-End Layer                                                           | . 44 |  |  |

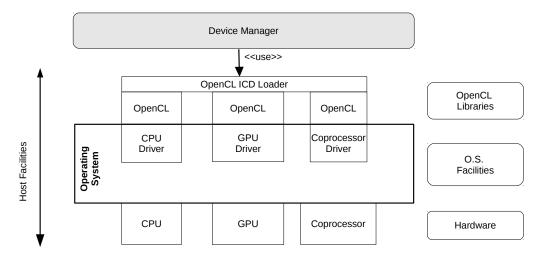

|    |     | 4.1.2 Back-End Layer                                                            | . 45 |  |  |

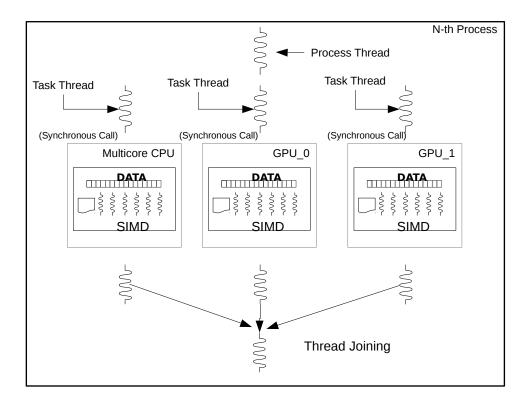

|    |     | 4.1.3 Execution View                                                            | . 47 |  |  |

|    | 4.2 | Programming with XSCALA                                                         | . 49 |  |  |

|    |     | 4.2.1 Tasks                                                                     | . 49 |  |  |

|    |     | 4.2.2 Data Dependencies                                                         | . 50 |  |  |

|    |     | 4.2.3 The XSCALA API                                                            | . 51 |  |  |

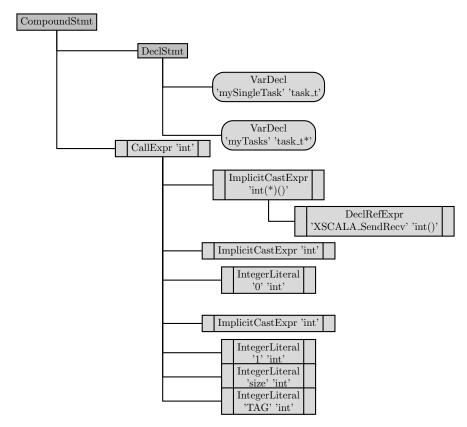

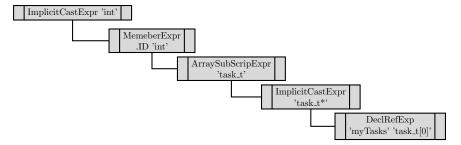

|    | 4.3 | Static Code Analysis                                                            | . 54 |  |  |

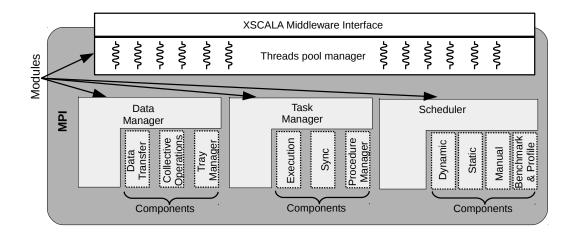

| 5  | XSO | ALA Middleware Architecture                                                     | 59   |  |  |

|    | 5.1 | Architecture                                                                    | . 59 |  |  |

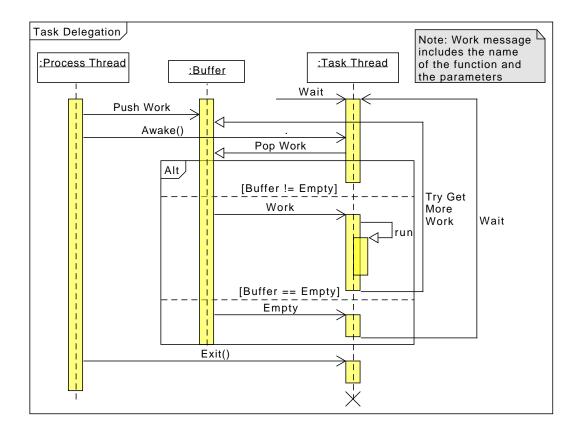

|    | 5.2 | The Threads Pool Manager Module                                                 | . 60 |  |  |

|    |     | 5.2.1 Task Delegation                                                           |      |  |  |

|    |     | 5.2.2 Dynamic Task Integration                                                  |      |  |  |

|    | 5.3 | The Task Management Module                                                      |      |  |  |

|    |     | 5.3.1 Procedure Management Component                                            |      |  |  |

|    |     | 5.3.2 Task Execution Component                                                  |      |  |  |

|    |     | 5.3.3 The Synchronization Component                                             |      |  |  |

|    | 5.4 | The Data Management Module                                                      |      |  |  |

|    |     | 5.4.1 Data Copy Component                                                       |      |  |  |

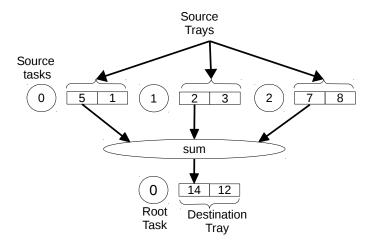

|    |     | 5.4.2 Collective Operations                                                     |      |  |  |

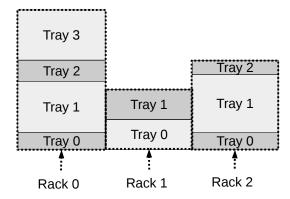

|    |     | 5.4.3 Tray Management                                                           |      |  |  |

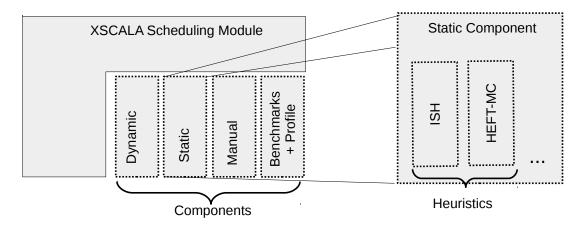

|    | 5.5 | The Scheduling Module                                                           |      |  |  |

|    |     | 5.5.1 Manual Scheduling                                                         |      |  |  |

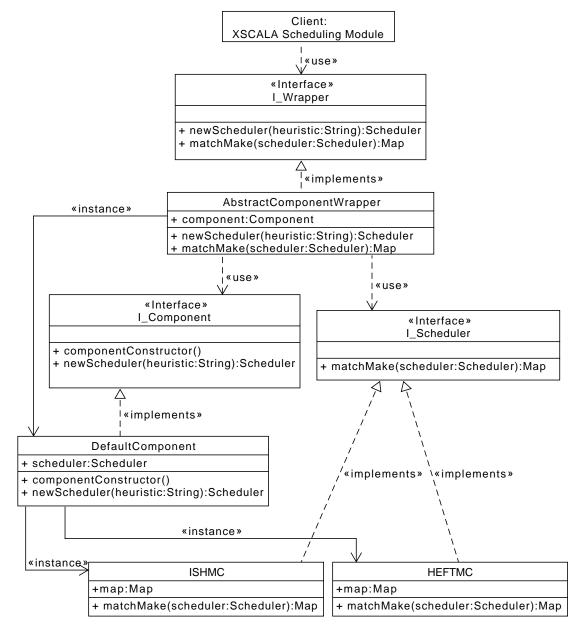

|    |     | 5.5.2 Static Scheduling Component                                               |      |  |  |

|    |     | 5.5.3 Dynamic Scheduling Component                                              |      |  |  |

|    |     | 5.5.4 Architecture of the Scheduling Component                                  |      |  |  |

|    |     | 5.5.5 Benchmark and Profiling                                                   |      |  |  |

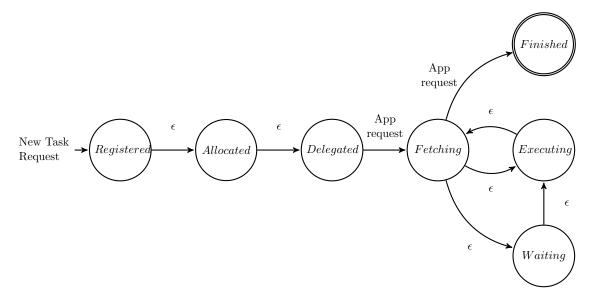

|    | 5.6 | Lifecycle of a Task in XSCALA                                                   |      |  |  |

|    | 5.7 | Correctness of the Execution                                                    |      |  |  |

| 6  | Sch | duling                                                                          | 85   |  |  |

|    | 6.1 | Static Scheduling Algorithms                                                    |      |  |  |

|    | -   | 6.1.1 The R res $1 \cdot \cdot \cdot$ , prec  $C_{max}$ , WS Scheduling Problem |      |  |  |

|    |     | 6.1.2 The HEFTMC Algorithm                                                      |      |  |  |

|    |     | 6.1.3 The ISHMC Algorithm                                                       |      |  |  |

|    | 6.2 | Dynamic Scheduling Algorithms                                                   |      |  |  |

|    |     | 6.2.1 RRMC Algorithm                                                            |      |  |  |

*Contents* xi

|              | 6.2.2 ESTMC Algorithm                   | 96  |

|--------------|-----------------------------------------|-----|

| II           | I Results                               | 97  |

| 7            | Experimentation and Results             | 99  |

|              | 7.1 Experimental Platforms              | 100 |

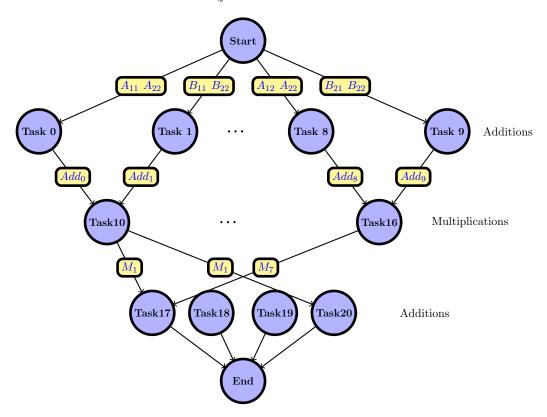

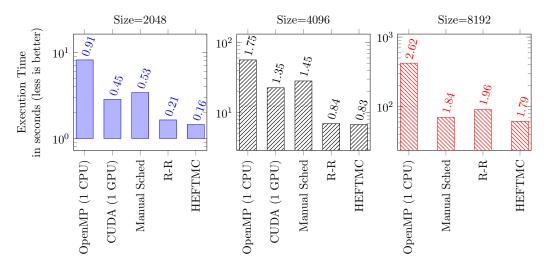

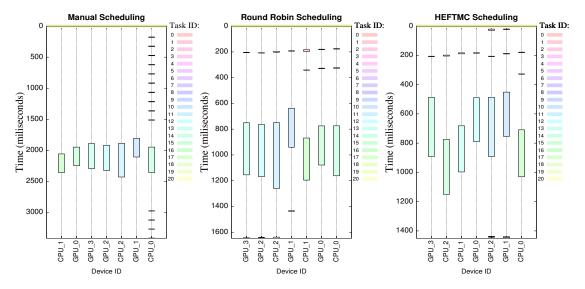

|              | 7.2 The Strassen Algorithm              | 101 |

|              | 7.3 Scalable Linear Algebra with XSCALA | 108 |

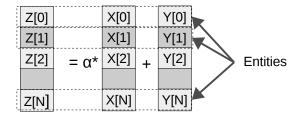

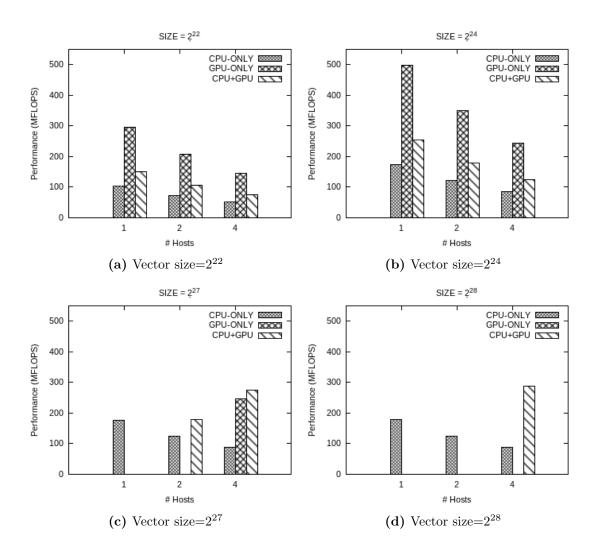

|              | 7.3.1 SAXPY                             | 109 |

|              | 7.3.2 SGEMM                             |     |

|              | 7.4 The N-Body Simulation Problem       |     |

| 8            | Conclusions and Future Work             | 123 |

| $\mathbf{A}$ | 112 CTILIT COMO SAMPIOS                 | 127 |

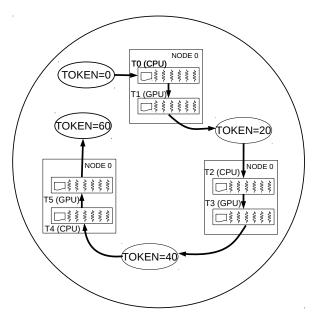

|              | A.1 Static Token Ring                   | 127 |

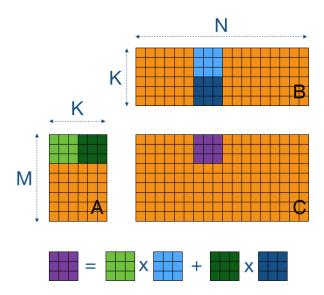

| В            | Tiled Matrix Multiplication             | 131 |

| ${f Bi}$     | bliography 1                            | 133 |

# Chapter 1

# Introduction

The use of hybrid memory cluster computing systems with heterogeneous accelerators has become the standard and most cost-effective approach for solving large scale scientific problems within reasonable amounts of time.

An hybrid memory cluster consists of several computers interconnected by a local network where each computer is equipped with one or more multicore processors. Each computer might be equipped with other types of general purpose processing units like GPUs or coprocessors accelerating the execution of certain tasks. The term hybrid refers to the combination of shared and distributed memory architectures commonly found in a cluster of workstations with multicore processors whereas the heterogeneity refers to the different capabilities and architecture of each processing unit. We will refer to this kind of system as an Hybrid Heterogeneous (H/H) computing system.

Exploiting H/H systems is a complex task that requires the combination of multiple programming tools and a careful distribution of the workload. For example: the shared memory model requires of tools like OpenMP or Pthreads, the distributed memory model requires of a communication middleware like MPI, and finally tools like CUDA or OpenCL are required to harness data parallelism in GPUs.

On the other hand, the performance achieved in the execution of an application is strongly related with the technique used for the distribution of the workload. Such distributions must avoid overloading a single computing device beyond its capabilities nor allocating tasks requiring intensive data communication in remote nodes connected through low bandwidth channels.

The problem of mapping tasks to devices in an optimal way is known as the scheduling problem and due to its complexity is strongly believed that there no exists an algorithm that can find optimal mappings using reasonable amounts of time. Several algorithms based on heuristics have been developed for specific cases providing good solutions in short amounts of time. A heuristic for scheduling will try to find a workload distribution that minimizes the total execution time using some fixed rules.

This complex scenario raises the necessity for a new programming model that can provide a higher level of abstraction of the underlying hardware hiding the complexity of H/H architectures.

The new programming model must be supported by libraries, compilers and runtime execution environments working together to simplify the development of applications and to provide services for the execution of applications.

A set of tools, models and strategies designed to solve an specific problem is referred to as "framework" and can fill the gap between efficient use of resources and ease of programming.

Some of the frameworks found in the literature [Kegel et al., 2012], [Barak et al., 2010], [Alves et al., 2013], [Takizawa et al., 2013], [Aoki et al., 2010], [Augonnet et al., 2011] extend the capabilities of OpenCL, a low-level API for heterogeneous computing, to support transparent internode communications trying to emulate a single "super node" with many devices attached to it. This kind of work are built on top of distributed shared memory systems. Among the major disadvantages of this approach is that distributed shared memory systems are known to be slower than asynchronous message passing systems [Kshemkalyani and Singhal, 2011], besides of this, many useful services provided by message passing middleware are hidden for example, distributed file management, collective communication routines and distributed atomic operations, those services result essential to perform coarse data distribution in cluster systems. Finally it is worthwhile to say that the OpenCL API is too verbose and complex to use.

Another approach found in the literature consists in extend the capabilities of the middle-ware, in particular, of MPI to ease the management of GPUs and coprocessors [Lawlor, 2009], [Song and Dongarra, 2012], [Gabriel et al., 2004a]. These works can perform efficient data transfers using sophisticated communication hardware in a transparent way to the programmer. However a major disadvantage of these works is that the scheduling problem is still delegated to the programmer who is also responsible for coordinate the execution of the application.

Finally there exists some extensions to other conventional tools for multithreading programming like OmpSS [Fernández et al., 2014], and OpenACC [El-Ghazawi et al., 2005a] that rely on compiler directives, code annotations, APIs, and runtime systems to simplify the development of applications that can readily offload parts of the application to

accelerators however they are limited to shared memory (only one computer) limiting the scalability of the applications.

With respect to the scheduling problem some works [Augonnet et al., 2011], [Grasso et al., 2014], [Vasudevan et al., 2013] implement a dynamic scheduling technique to distribute the workload. In dynamic scheduling the tasks are dispatched at runtime using a centralized pool of tasks where the scheduler can distribute the work using fixed policies for example, finding the fastest computing device or the one that minimizes data transfer costs. Although this strategy has been thoroughly studied before [Cybenko, 1989], [Maheswaran et al., 1999], [Shirahata et al., 2010], [Cederman and Tsigas, 2011], and has proved to be very efficient in getting mappings it also have some disadvantages that must not be overlooked for example, a dynamic scheduler cannot anticipate future workloads which might in turn rise a performance degradation due to the possibility of premature overloading of the faster computing device, furthermore, the scalability of the applications is limited by the capabilities of the scheduling server.

The hypothesis that we hold in this work is that the parallel task programming model is a better approach to deal with the difficulties arising in H/H programming pointed out before. To assert the validity of this statement we present XSCALA (*Xplatform SCALAble*) a framework to support parallel task programming.

The objectives of XSCALA are twofold: simplify the development of applications adaptable to different computing environments and scalable as more hardware is used, and provide the mechanisms to ensure an efficient use of the computing resources.

To address the problem of load balancing we propose the integration of multiple scheduling strategies, in particular, we explore the advantages of static scheduling algorithms. Static scheduling can improve the performance of the applications with respect to dynamic scheduling due to the possibility of combine the analysis of the data dependencies with benchmark information to propose a plan of execution. Another advantage of static scheduling is a better use of the memory resources, a scarce resource that must be used and freed as soon as possible to use it in other tasks.

The major disadvantage of static scheduling is the large amount of information required to execute the algorithms. To overcome this problem all information required to perform static scheduling is automatically collected from the source code of the applications using a static analyzer plugin and from other performance evaluations for example: the compute capability of each device, latency in communications, and the bandwidth between each pair of processing units.

Finally to satisfy the trade-off between ease of programming and efficiency our framework introduces an API for task programming with functions resembling the MPI API which eases the learning process.

In order to demonstrate the advantages of the XSCALA framework and the degree of success achieved in our objectives we implemented all the components of the framework as well as several applications to measure the performance, overhead, and ease of programming achieved with our solution.

The major contributions of this work to the state of the art are the design of the framework architecture for supporting parallel task programming in hybrid heterogeneous environments, and the integration of new algorithms for the solution of concurrency and scheduling problems.

Among the applications used to test the framework we have linear algebra operations and the N-Body problem. We executed those applications using multiple platforms representative of the execution environments supported by XSCALA.

We compared the lines of code required for the implementation against the traditional approaches as well as the performance achieved in each execution. We found that using our tool the number of code lines is dramatically reduced while eases considerably the distribution of workload bringing portability to the applications. We also found that the scalability is achieved when the applications have the size or the granularity enough to hide latency cost.

This work is organized in three parts: context (chapters 2 and 3), contributions (chapters 4, 5, and 6), and results (chapter 7).

In chapter 2 we present the basic concepts and notation related to the use of parallel computers and the problems arising in this field. In the chapter 3 we review the state of the art in approaches for hybrid heterogeneous programming emphasizing on the relevant features of each work.

In the chapter 4 we present the architecture of the XSCALA framework including a description of each layer, its objectives, and its internal architecture. Next we presents our concept of the parallel task programming model and the functions defined in our API.

In chapter 5 we present the internal architecture of the middleware layer, its components and the algorithms implemented to solve the concurrency problems inherent in parallel programming. We also present formal definitions of the issues that entails to support the parallel programming model.

In chapter 6 we present our approach to solve the scheduling problem for H/H architectures with resource constraints. We present the scheduling algorithms proposed including a discussion of its complexity.

In the chapter 7 we present the implementation of some applications including linear algebra, the N-Body problem. There we show how to use our framework, and the reduction in the number of code lines. We performed several experiments varying the size of the problem and the scheduling technique.

Finally in the chapter 8 we present the conclusions and the future directions of this work.

Part I

Context

# Chapter 2

# Background

In this chapter we present a brief description of the concepts required to understand the scope and context of this work. Our intention consists in give a landscape view of what parallel programming for hybrid heterogeneous systems means and how can it be accomplished.

### 2.1 Basic Concepts

In this section we present the definitions of middleware and framework used to describe the components in our proposal and the concepts of scalability and portability used to understand the features desired in this work.

#### 2.1.1 Middleware

Middleware is a software layer designed to provide an abstraction of another underlying software enabling the development of modular system architectures [Krakowiak, 2007]. There exists several types of middleware designed for specific purposes for example: message oriented middleware, grid middleware, database middleware, QoS middleware, remote procedure call (RPC) middleware, object request brokers (ORBs), etc.

Middleware is fundamental in the context of distributed applications where provides distributed services like naming, messaging, fault tolerance, process spawning, among others with the aim of enable multiple processes running on one or more machines to interact across a network. The middleware layer in distributed systems sits above the network operating system and below the application hiding the heterogeneity of the communication system [Bernstein, 1996].

RPC systems and ORBs middlewares deal with the distribution of the workload by requesting the execution of procedures or methods to other peers in the network. This approach results specially beneficial for applications that can delegate the execution of the hardest parts to other specialized peers.

Message oriented middleware employs peer-to-peer relationships between individual peers, where each peer can send and receive messages to and from other peer [Curry, 2004]. Message oriented middleware can be implemented using a message delivering approach like MPI. This approach is suitable to solve scientific problems dealing with big amounts of data, letting each node work with a chunk of the data.

#### 2.1.2 Frameworks

A Framework is an integrated set of components that collaborate to provide a reusable solution for a family of related problems. A formal definition of the concept is given by Smith [Schmidt et al., 2000] that defines a framework as a concrete realization of patterns that facilitate direct reuse of a detailed design. In this definition a pattern describes a particular recurring problem that arises in specific contexts and a well proven generic scheme for its solution *i.e.* the "best practices" for solving the problem. The solution scheme is specified by describing its constituent components, their responsibilities and relationships.

Among the components integrating a framework we have:

- Application programming interfaces.

- Libraries.

- Runtime systems.

- Middlewares.

- Compilers, wrappers and pre-processors.

An Application Programming Interface (API) is a flat collection of function specifications, wrapping routines, and protocols with frequently used functionality [Buschmann et al., 1996]. APIs usually can be found in the form of header files and documentation.

Libraries and runtime systems are implementations of the functions described in the API but libraries differ from runtime systems in that the former performs a specific function when is requested by the main program while the latter provides a set of functions executed before, during, and after the execution of the main program. The functions

contained in the libraries and runtime systems can be requested by the applications using the API, although some of the functions might be hidden to the programmer and are used internally to provide services like task scheduling, resource management, among others.

Some frameworks include tools to build the applications for example, compilers, wrappers and other code preprocessors. Some examples of this kind of tools are the *Nvidia c compiler* [Nickolls et al., 2008], the *OpenMPI c compiler* [Gabriel et al., 2004a].

#### 2.1.3 Portability

Portability refers to the degree to which an application can be moved from one execution environment to another achieving the same results [Marowka, 2010]. In the high performance computing field the portability is also related with the capability to achieve similar performance when the application is executed in different environments with similar capabilities, this kind of portability is referred to as performance portability.

#### 2.1.4 Scalability

Scalability is the capability to get an increase in performance of a specific application as more hardware resources are added [El-Rewini and Abd-El-Barr, 2005]. There exists two types of scalability:

- Strong scalability: The total problem size stays fixed as more processors are added.

- Weak scalability: The problem size per processor stays fixed as more processors are added.

Scalability is one of the most important nonfunctional requirements for several applications of HPC given that enables harnessing all the resources available for the execution.

## 2.2 Parallel Computer Memory Architectures

In this section we present a classification of parallel computers based on their memory architecture. We present the most remarkable features of each class of memory architecture namely: shared memory, distributed memory, and hybrid memory.

#### 2.2.1 Shared Memory Architectures

Computers with shared memory architecture have a common memory accessible to a number of physical processors interconnected by fast local buses (e.g. cross bar or QPI). Communication between tasks running on different processors is performed by writing and reading to the global memory space [El-Rewini and Abd-El-Barr, 2005].

There exists two classes of shared memory architectures: Uniform Memory Access (UMA) and Non-Uniform Memory Access (NUMA) [Herlihy and Shavit, 2012]. Computers having one multicore processor are examples of UMA architectures where multiple identical "cores" have equal access time to the shared memory space. A computer having two or more processors on the same board is an example of NUMA architecture where each core of each processor have fast access to "near" shared memory space and slow access to "remote" shared memory space.

#### 2.2.2 Distributed Memory Architectures

Distributed memory architectures are systems composed of a number of networked computers each with its own local processing resources and separate memory spaces using a communication protocol to share data and coordinate their actions [Coulouris et al., 2011]. An example of this type of architecture are commodity clusters, which consists of several workstations connected by a local area network (LAN) using the message passing interface (MPI) to share data. This approach has proven to be a cost-effective solution for certain problems of large scale like simulations or climate forecasting.

#### 2.2.3 Hybrid Memory Architectures

Hybrid memory architecture refers to the combination of shared and distributed memory architectures [Herlihy and Shavit, 2012]. This type of architectures are built by connecting several workstations in a LAN with each computer having shared memory architecture itself for example, it might have one or more multicore processors.

# 2.3 Heterogeneous Computing Architectures: GPUs and Coprocessors

A cluster computer is heterogeneous when its processing units have different characteristics or capabilities. This diversity is the result of the accumulation of multiple computing resources some of them specialized in the execution of some tasks.

The objective behind this accumulation of resources is to reduce the time required to get a solution (strong scalability) or to solve bigger problems within a reasonable amount of time (weak scalability) [Dongarra and Lastovetsky, 2009]. A cluster of computers is defined as heterogeneous if some of the following conditions are meet:

- Processors in the cluster are not identical neither in architecture nor in capabilities.

- The communication network may have a regular architecture but with heterogeneous components. For example, it might consists of a number of faster communication segments interconnected by relatively slow links. Such a structure can be obtained by connecting several homogeneous clusters in a single multicluster.

- The cluster may be a multitasking computer system, allowing several independent users to run simultaneously their applications on the same set of processors (but still dedicated to high-performance parallel computing).

Nowadays, each node in a cluster-computer is equipped not only with traditional CPUs but with other general purpose computing units like graphical processing units (GPUs) or coprocessors having multiple cores wired in special configurations, designed to accelerate the execution of certain tasks.

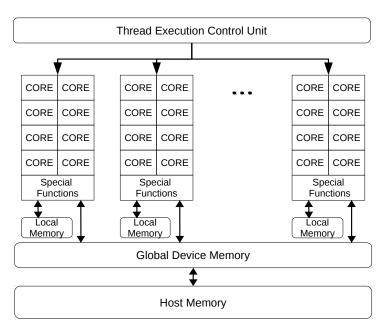

GPUs are computing devices capable of running thousands of lightweight threads in parallel [Kirk and Hwu, 2016]. The typical architecture of a GPU is depicted in Figure 2.1. GPUs are specially suited for the execution of simple but repetitive tasks due to the presence of hundreds or thousands of cores managed from a single control unit. In order to exploit the computing power of GPUs the programmer is encouraged to make a careful planning of the work avoiding thread divergence and coordinating the access to multiple memory hierarchies with different sizes and speeds.

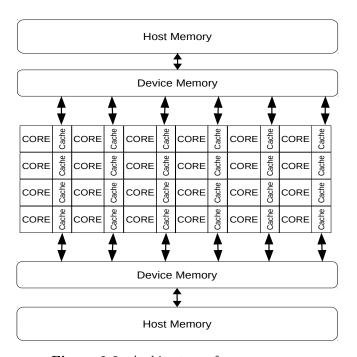

Coprocessors are other type of general purpose computing device similar to GPUs but with a smaller amount of cores, instead, coprocessors have tens of independent cores capable of running more complex and even divergent tasks [Jeffers and Reinders, 2013]. Each core have fast access to large amounts of local memory within the device and larger amounts of cache than in the GPUs. The architecture of a coprocessor is depicted in Figure 2.2.

GPUs and coprocessors have its own Instruction Set Architecture (ISA) requiring the use of cross compilers to generate machine code suitable for each architecture. The necessity of building machine code specific for each architecture rises a serious limitation to the portability of the applications thus requiring recompilation of applications and the use of specific development tools for each vendor.

Figure 2.1: Architecture of a GPU.

Figure 2.2: Architecture of a coprocessor.

Hereinafter we will use the terms "host" or "node" interchangeably to refer to each one of the computers in the cluster and the terms "processing unit (PU)", "processing element (PE)" or "device" will be used indistinctly to refer to any processing unit regardless of its architecture. The concept of heterogeneity will refer to both: the diversity in the capabilities of each device and the diversity in the instruction set of the processing units. Finally the term hybrid heterogeneous (H/H) cluster will refer to a cluster of computers interconnected through a local network with each node equipped with one or more heterogeneous processing units.

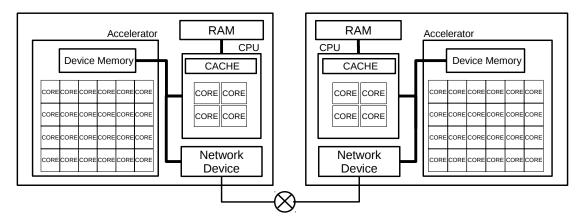

An example of H/H system is depicted in Figure: 2.3 with two nodes connected through a network device where each node have two processing units: a multicore CPU, and a many core accelerator. The major advantage of this kind of architectures is that they can be readily extended to thousands of nodes in the network with several CPUs or accelerators for each node.

Figure 2.3: Architecture of an hybrid heterogeneous (H/H) computing system.

## 2.4 Parallel Programming Models

In its more general form a *programming model* consists in the definition of certain structures and their relationships to provide an abstraction of the underlying hardware with the aim of ease the design and implementation of algorithms.

The major objective of a programming model is to let the programmer or the algorithm designer to assume that certain events just happens and do not be carried about how they actually happen. For example, in task programming the programmer can assume that each task will be eventually executed in a processing unit no matter which and that the data transfers will be eventually completed no matter how.

Parallel programming models are a class of programming model specially useful in the design of applications where it is possible to take advantage of the replication and distribution of work among several execution units with the objective of achieve a faster execution. Each model might in turn define its own execution units for example threads or processes.

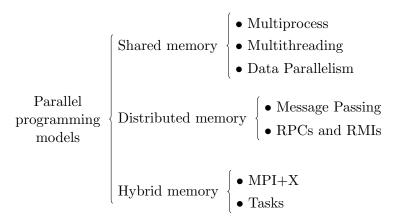

Parallel programming models can be classified based on the abstraction of memory hardware that they make [Balaji, 2015] i.e shared memory, distributed memory or hybrid memory. This classification and some examples of each class is depicted in Figure: 2.4.

Figure 2.4: Classification and examples of parallel programming models.

#### 2.4.1 Shared Memory Programming Models

This class of programming models are specially designed for shared memory architectures where each execution unit have a local unified view of all the data of the application.

#### Multiprocess and Multithreading

Multiprocess and multithread programming are two types of programming models based on the idea of let two or more execution units namely: processes in the case of the former and threads in the case of the latter to interact along the execution of the application [Raynal, 2012], [Herlihy and Shavit, 2012]. Therefore, the processes of a multiprocess application and the threads in a multithread program may execute simultaneously ("in parallel" or "concurrently") parts of the same program. This two programming models are strongly related due to the problems and techniques used to solve synchronization issues hence they are commonly refereed to as "concurrent programming"

The major concern in concurrent programming is the problem of synchronization that occurs when the progress of one or several processes (threads) depends on the behavior

of other processes (threads). More generally, synchronization is the set of rules and mechanisms that allows the specification and implementation of sequencing properties on statements issued by the processes (threads) so that all the executions of a multiprocess (multithread) program are correct [Raynal, 2012].

Concurrent programming is specially suited for shared memory architectures where the processes (threads) have fast and secure access to several forms of locking and synchronization structures (e.g., mutexes, semaphores, or monitors) to coordinate the execution of the program. Some canonical programming tools supporting multithreading are OpenMP and Pthreads whereas multiprocess must be implemented using libraries and tools provided directly by the operating system.

#### Data Parallelism

The data parallel model also referred to as the Partitioned Global Address Space (PGAS) model consists in a set of execution units having access to a global address space, where each execution unit performs the same operation on a different partition of the data [Kirk and Hwu, 2016].

This model is well suited for problems exhibiting coarse grained parallelism where a large number of operations can be performed without requiring neither synchronization nor messaging between the execution units but must avoid task divergence.

This model requires the design of the applications in such a way that the selection of a block size do not compromises the correctness of the algorithm offering great scalability at the cost of making the programmer responsible for ensure the correctness of his program regardless of the distribution of the array between the execution units.

Some programming tools supporting data parallelism are  $Unified\ Parallel\ C\ (UPC)$  [El-Ghazawi et al., 2005b] and  $thread\ building\ blocks$  [Reinders, 2007].

#### 2.4.2 Distributed Memory Programming Models

#### Message Passing

The message passing programming model consists in several networked processes using their own local memory space and communicating with each other using messages. Each process is attached to one computer and can be any number of physical computers hosting the processes (even only one) [Coulouris et al., 2011]. The message passing

model is specially suitable to achieve weak scalability due to the possibility to add more computers to the network in order to solve problems with more data.

Communication in this model is typically done using send/receive pairs of commands, broadcasting and other communication primitives but there is no concept of global memory space, therefore, synchronization is also performed using messages from one local memory space to all others making this process slow and more complex than in the shared memory approach.

#### RPC and RMI

Remote procedure call (RPC) and remote method invocation (RMI) are other two programming models used to achieve parallel execution of work. An application using remote objects is typically organized in a client-server approach: a process or thread executing a method of a client object sends a request to the server object to execute a method of that object [Tanenbaum and van Steen, 2007], [Coulouris et al., 2011].

Although RPC and RMI were not specifically designed for parallel programming they can achieve parallelism by letting the caller to perform multiple calls to the server (or create several objects in the case of RMI) while the server side administrates several parallel execution units serving the requested methods. This programming model is used in works like charm++ Kale and Zheng [2009] enabling it to provide other useful services like fault tolerance and load balancing.

#### 2.4.3 Hybrid Memory Programming Model

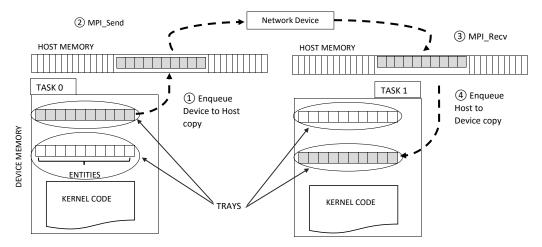

A hybrid programming model have the objective of exploit the advantages of multiple models by combining some of them. In particular, the combination of the message passing model with other model for shared memory programming is referred to as the MPI+X programming model [Quinn, 2004].

The hybrid programming model is currently the most common approach to harness H/H systems. This model consists in a coarse separation of the data to be processed among multiple MPI processes located in different machines followed by groups of threads in GPUs or coprocessors performing computationally intensive tasks using local on-node data. Some typical examples of the tools used to support hybrid programming models includes MPI+OpenMP, MPI+CUDA, MPI+OpenCL, and MPI+OpenMP+CUDA.

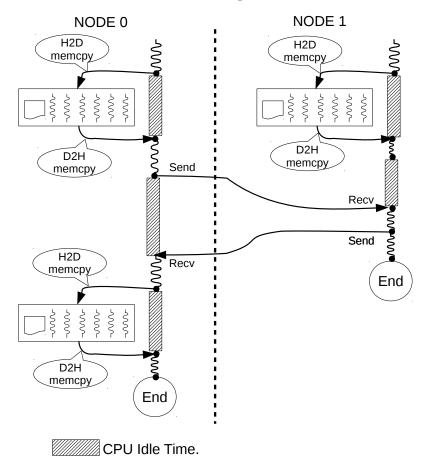

The hybrid programming model is depicted in the Figure: 2.5 where we show two nodes executing one application that offloads parts of the computation to the devices. The

transfers of data from the host to the device (H2D) and conversly (D2H) is requested by the application as well as the send and receive operations for internode communications.

**Figure 2.5:** MPI+X procedural programming model. Portions of the computation are offloaded to the processing units using explicit data transfers and execution requests. Internode communications are completed through messages.

The major disadvantage of the hybrid approach is the complexity associated with the combination of multiple tools as well as the difficulty to achieve an efficient execution. The use of synchronous calls in the delegation limits the scalability of this approach to one device per node. When multiple devices are attached to the node the model requires an additional tool to implement threads and callback functions to enable the use of asynchronous calls.

## 2.5 The Parallel Task Programming Model

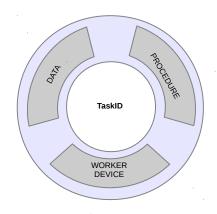

The task programming model is a high level programming model based on the construction and distribution of small units of work called "tasks".

The most remarkable feature of task programming is that tasks are self-contained, in the sense that they can be executed and completed by a batch of threads entirely without

requiring intervention of other tasks. The tasks are linked through data dependencies establishing in this way the order of execution.

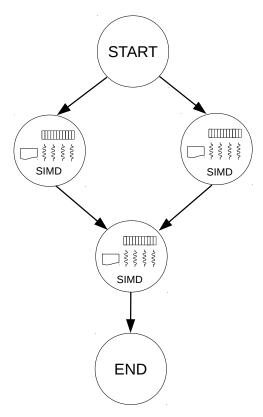

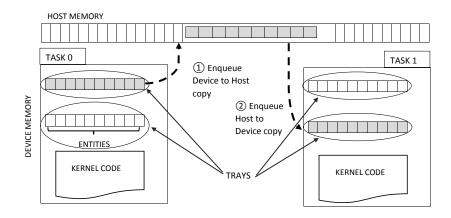

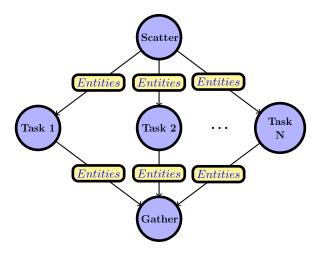

The task programming model can take full advantage of H/H systems by exploiting both: coarse grained parallelism and fine grained parallelism. The former is achieved by launching multiple tasks to be executed concurrently or in parallel using multiple devices and the latter consists in launching several threads using the Single Instruction Multiple Data (SIMD) model on each task to complete the work. This model is referred to as parallel task programming and is depicted in the Figure: 2.6.

**Figure 2.6:** The task programming model. Data is transferred automatically between the devices regardless of their location and a scheduler can assign the tasks to the most suitable device.

Unlike the MPI+X approach where the programmer is responsible for offloading portions of the application into specific processing units and take care of synchronization issues the parallel task approach provides a higher abstraction of the underlying computing system handling many of these problems in a transparent and efficient way for example, the data transfers are overlapped with the computation and the tasks are assigned to the most suitable device.

#### 2.5.1 History and Advances

The adoption and implementation of the task model is relative more recent than other paradigms like structured and object oriented programming. This is partly explained because they were expressive enough for the bast majority of algorithms while provided an enough level of abstraction of the most common computing architectures.

In 1993 Rinard presented JADE [Rinard et al., 1993], one of the first works in the task programming direction, remarking that some task may require special hardware to enable its execution or to accelerate its completion.

More recently the OpenMP standard advanced in the task programming trend. OpenMP is a specification<sup>1</sup> for a set of compiler directives, library routines, and environment variables that can be used to specify high-level parallelism. Since release 3.0 the OpenMP specification was extended to incorporate support for task-based parallelism in shared memory multiprocessor architectures [Ayguadé et al., 2008], [Ayguadé et al., 2009].

Another languages and execution environments have been extended to support task parallelism for example, the task parallel library in microsoft .NET [Leijen et al., 2009] or intel Thread Building Blocks (TBB) [Reinders, 2007], that are libraries supporting the task programming model in multicore processors.

#### 2.5.2 Representation of Workflows with Graphs

The sequence in which the execution control is transferred from task to task is referred to as *workflow* and can be represented with graphs.

A graph G is composed of a non-empty finite set V(G) of elements called vertices and a finite set E(G) of distinct unordered pairs of elements of V(G) called edges [Wilson, 1996]. Therefore a graph G is defined as a pair (V, E) where V is called the vertex set and E the edge set. An edge is an unordered pair  $\{v, w\}$  joining the vertices v and w of V, and we say that vertex v and w are adjacent if  $\{v, w\} \in E$ .

Directed graphs (or digraphs) differ from graphs in that the former is defined in terms of ordered pairs thus making the edge (v, w) different from the edge (w, v) when both are in E. In digraphs the out-degree of a vertex is the number of edges leaving it, and the in-degree of a vertex is the number of edges entering it [Cormen et al., 2001].

<sup>&</sup>lt;sup>1</sup>OpenMP Architecture Review Board (Ed.) (2008, May). OpenMP Application Program Interface. Retrieved September 18, 2016, from http://www.openmp.org/wp-content/uploads/spec30.pdf Version 3.0

A weighted graph  $G_c = \{V, E, c\}$  is a graph where each edge  $e \in E$  has an associated weight given by a weight function  $c : E \to \mathbb{R}$ . The vertices in a graph can have weights instead of or besides to the weights of the edges [Wilson, 1996]. A graph having weighted vertices will be denoted as  $G_w = \{V, E, c, w\}$ .

We can represent the resources available in a computing system with the graph  $G_r = \{V_r, E_r, c_r\}$  were each vertex  $v \in V_r = \{PU_1, PU_2, ..., PU_n\}$  denotes a processing unit, each edge  $e \in E_r = \{C1, C2, ..., C_k\}$  denotes a communication link between two processing units, and  $c_r : E_r \to \mathbb{R}$  represents the bandwidth between each pair of PUs.

Similarly, we can use a weighted graph  $G_t = \{V_t, E_t, c_t, w\}$  to represent the workflow of any given application. Here the vertex set  $V_t$  represents the set of task to be executed, the edge set  $E_t$  represents the data dependencies between tasks,  $c_t : E_t \to \mathbb{R}$  represents the amount of data to be transferred between to tasks and  $w : V_t \times V_p \to \mathbb{R}$  represents the cost of executing any give task of  $V_t$  in a processing unit of  $V_p$ .

Many scientific problems can be solved based on the definition of tasks and the accumulation of the results, furthermore there exists some basic patterns to express workflows [van der Aalst et al., 2003], and many others can be implemented using combinations of them.

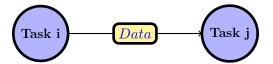

#### Sequence

Sequence is the most common pattern and establish the consecutive steps in a workflow as is depicted in the figure 2.7. In this pattern the task j can start only after the arrival of the data coming from the task j. In this case we say that the task i is the predecessor of j or that the task j is the successor of i.

Figure 2.7: The sequential pattern.

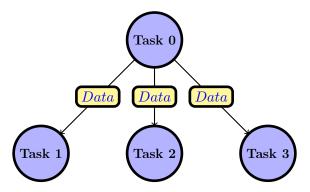

#### Parallel Split

Parallel splits are points in the workflow where one executing task can activate the execution of more than one successors. The new activated tasks can be executed concurrently or in parallel as is depicted in the Figure: 2.8.

Figure 2.8: Workflow with a parallel split.

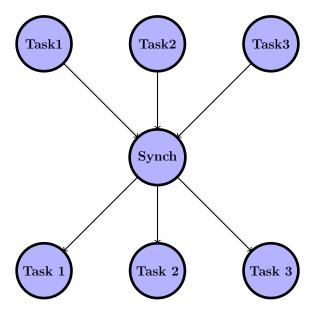

#### Synchronization

Synchronization are points in the workflow where multiple independent tasks converge without require additional data transfers among them. This pattern is depicted in figure 2.9. This pattern is useful to ensure that each task has reached certain state before to proceed to the next operation.

Figure 2.9: Workflow with a synchronization point.

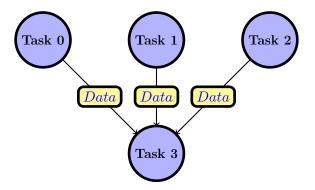

#### Single Merge

Single merge patterns are points in the workflow where a single task have data dependencies form two or more branches of the graph. This pattern is depicted in figure 2.10.

Figure 2.10: Workflow with a merge.

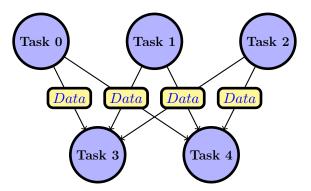

#### Multiple Merge

Multiple merge patterns are points closely related to single merges but in this case there exists two or more tasks in the DAG having common dependencies fulfilled at the same time as is depicted in figure 2.11.

Figure 2.11: Workflow with multi merge.

### 2.6 Scheduling

The performance achieved in the execution of an application is strongly related with the technique used for scheduling tasks. In this section we present a formal definition of the scheduling problem and a classification of the scheduling techniques based on the features of the problem.

#### 2.6.1 Classification of Scheduling Algorithms

Let  $G_r$  and  $G_t$  to represent the resource and task graphs as previously defined in section 2.5.2. A task mapping M is defined as a set of ordered pairs  $\{(i,j) \mid i \in V_t, j \in V_p\}$

where each ordered pair (i, j) reflects the assignment of the task i to be executed in the processing unit j.

The task scheduling problem consists in finding the mapping M that minimizes the completion time of all the tasks in  $G_t$  subject to certain constraints. A naive approach to solve this problem is testing all combinations but it could take up to  $m^n$  evaluations with  $m = |V_r|$  and  $n = |V_t|$ . This number of evaluations talks about the difficulty of the problem, furthermore, the general formulation of the task scheduling problem is known to be an NP-complet problem [Gary and Johnson, 1979].

The scheduling problem have several specific variants depending on the constraints, the number of processors and the features of the tasks, however, very few of them can find optimal solutions using polynomial time algorithms [Brucker, 2013]. Given the complexity of the problem many algorithms based on heuristics have been formulated to construct "good" mappings for complex cases of the problem using a reasonable amount of time.

Scheduling algorithms can be broadly divided depending whether the mapping decisions are taken at runtime (dynamic scheduling) or at compile time (static scheduling). The former is appropriate when neither the amount of task to be executed nor the data dependencies among them are known beforehand, and the latter can improve the application performance due to its ability to take mapping decisions based on the characteristics of the tasks, the data dependencies and the capabilities of the computing resources.

The classification of the scheduling algorithms can be further divided depending on whether they consider or not data dependencies, if preemption is allowed, or if they consider or not heterogeneous resources. Given the overwhelming amount of variations of the scheduling problem Graham [Graham et al., 1979] introduced a scheme known as three field notation  $\alpha |\beta| \gamma$  to classify the scheduling problems.

This classification assumes that n Jobs  $J_1 \ldots, J_n$  have to be processed on m machines  $M_1, \ldots, M_m$ , where each machine can handle at most one job at a time and each job can be executed by at most one machine at a time. Some possible values of the parameters  $\alpha, \beta, \gamma$  are as follows:

The field  $\alpha$  specifies the architecture of the computing system and have two components denoted by  $\alpha_1, \alpha_2$ . Some possibles values for  $\alpha_1$  are  $\{P, Q, R\}$  where:

- $\alpha_1 = P$  indicates parallel identical machines.

- $\alpha_1 = Q$  indicates parallel uniform machines.

- $\alpha_1 = R$  indicates parallel unrelated machines.

And  $\alpha_2$  is an optional positive integer equal to m.

The field  $\beta$  is a list of values indicating job characteristics where: "pmtn" indicates if preemption is allowed, "prec" indicates precedence constrains, and "1" indicates that each operation has unit processing time.

Finally the third field denotes the optimality criterion. Some common criteria are:

- $C_{max} = max\{C1, \dots, C_n\}$  (maximum completion time)

- $\sum C_i = C1 + \ldots + C_n$  (total completion time)

$C_{max}$  is the most widely used criteria and is known as the makespan of the application.

Some representative scheduling algorithms based on heuristics includes the minimum completion time (MCT), the opportunistic load balancing (OLB) [Armstrong et al., 1998], minimum execution time (MET), the min-min heuristic [Braun et al., 2001], insertion scheduling heuristic (ISH), bubble scheduling and allocation (BSA) [Kwok and Ahmad, 1999], dynamic level scheduling (DLS) [Sih and Lee, 1993], modified critical path (MCP) [Wu and Gajski, 1990], heterogeneous earliest finish time (HEFT) [Topcuouglu et al., 2002], dynamic critical path (DCP) [Kwok and Ahmad, 1996], Highest Levels First with Estimated Times (HLFET) [Adam et al., 1974].

The classification of those algorithms and the problems that they solve is summarized in the Table 2.1.

|                       | Scheduling problem  | Scheduling algorithms  |

|-----------------------|---------------------|------------------------|

| ic<br>ing             | $P  C_{max}$        | Round Robin            |

| Dynamic<br>Scheduling | $R  C_{max}$        | Work Stealing          |

|                       | $R  C_{max}$        | Diffusion              |

|                       | $Q  C_{max}$        | Priority Queue         |

|                       | $P prec, 1 C_{max}$ | Hu's algorithm         |

| <u>బ</u>              | $Q  C_{max}$        | OLB, MET, MCT, min-min |

| ic<br>Ilin            | R prec Cmax         | HEFT                   |

| Static<br>Scheduling  | P prec Cmax         | ISH                    |

|                       | P prec Cmax         | DCP                    |

|                       | P prec,pmtn Cmax    | HLFET                  |

|                       | R prec Cmax         | DLS                    |

Table 2.1: Classification of Scheduling Algorithms

Static scheduling for tasks with data dependencies and without loops is a special case of the scheduling problem that has been thoroughly studied in the literature using priority lists. In spite of the complexity of the scheduling problem some algorithms based on priority lists [Hu, 1961], [Sih and Lee, 1993], [Yang and Gerasoulis, 1994], [Topcuouglu

et al., 2002] can obtain quasi-optimal schedules modeling the problem with directed acyclic graphs (DAGs) and sorting the tasks based on certain priority rules.

#### 2.6.2 Scheduling Subject to Constraints

When the execution of a task is restricted by the availability of one ore more scarce resources we say that the scheduling problem is subject to resource constraints. Blazewicz [Blazewicz et al., 1983] proposed an extension to the three field classification schema to aggregate the restrictions in the availability of a resurce to the  $\beta$  parameter as "res $\lambda\sigma\varrho$ " where:

- $\lambda$  is a positive integer representing the number of scarce resources.

- $\sigma$  is a constant positive integer indicating that all the resources have an equal initial size; when it is not explicitly indicated a matrix s must be provided in the problem specification to indicate the initial amount of each resource on each device.

- $\varrho$  is a constant positive integer indicating that all resource requirements are equal in size; when it is not explicitly indicated an additional matrix r must be provided to indicate the requirement of each resource on each task.

#### 2.7 Performance Indicators

Performance refers to the degree of success in the execution of a task with respect to certain measure [Dongarra and Lastovetsky, 2009], [McCool et al., 2012] for example: the rate at which tasks are computed (throughput) or the time that takes to complete a task (latency).

The principal objective to use parallel computers is to improve the performance of applications regardless of the specific measure. This implies an iterative process that requires the use of certain metrics to compare the degree of improvement achieved on each step.

The two metrics commonly used are speedup and efficiency. The speedup compares the time that it takes to solve certain problem using one execution unit against the time required to solve the same problem using P processing units, i.e.:

$$speedup = S_p = \frac{T_1}{T_p} \tag{2.1}$$

Where  $T_1$  is the time required using one execution unit (also known as the sequential execution) and  $T_p$  is the time taken using P execution units.

The efficiency refers to the degree at which we are exploiting new added resources. Efficiency is computed dividing the speedup by the number of execution units i.e:

$$efficiency = \frac{S_p}{P} = \frac{T_1}{PT_p} \tag{2.2}$$

The use of processing units at full of its capacity yields an efficiency equal to one however this is seldom possible due to the overhead generated by communications and synchronization between the execution units as well as the existence of parts inherently sequential in the applications. The Amdahl law [Amdahl, 1967] establishes that exists an upper bound in the maximal speedup that can be achieved when adding resources to solve a problem given by:

$$S_p \le \frac{1}{f + (1 - f)/P} \tag{2.3}$$

Where f represents the fraction of sequential execution of the application and P the number of execution units. In particular when f tends to infinity we have that:

$$S_{\infty} = \frac{1}{f} \tag{2.4}$$

Which demonstrates the existence of such limit. Achieving the best performance subject to the Amdahl constraint represents a form of strong scalability.

On the other hand the Gustafson-Barsis' law [Gustafson, 1988] makes an important observation: "the speedup must be measured by scaling the problem to the number of processors, not by fixing the problem size." This observation is interpreted as follows: let W' = fW + (1-f)nW to be the workload of the problem with the parallelized fraction scaled by a factor of n thus the processing time using n execution units is given by:

$$T_n = \frac{fW}{1} + \frac{(1-f)nW}{n} = fW + (1-f)W \tag{2.5}$$

Therefore the theoretical speedup achieved using n processing units is given by:

$$S_n = \frac{fW + (1 - f)nW}{T_n} = f + (1 - f)n \tag{2.6}$$

Escaping thus the theoretical limit to the speedup imposed by Amdahl's law. The Gustafson-Barsis' law represents the weak scalability.

# Chapter 3

# The State of the Art

The development of applications able to harness H/H computing systems is a complex task requiring a deep knowledge of the architecture of the system being used and of multiple programming tools. This problem rises the necessity of new tools that can hide the complexity of the underlying system easing the development of portable applications that can scale as more hardware is added even if it is heterogeneous.

Among the proposals found in the literature to solve the H/H programming problem the most common consists on extend the capabilities of OpenCL to perform transparent communication between the processing units even if they are located on multiple hosts [Grasso et al., 2014], [Kegel et al., 2012], [Aoki et al., 2010], [Kim et al., 2012], [Alves et al., 2013], [Takizawa et al., 2013].

Other common approach is extending the capabilities of MPI to ease the management of heterogeneous computing devices [Lawlor, 2009], [Aji et al., 2012], [Song and Dongarra, 2012].

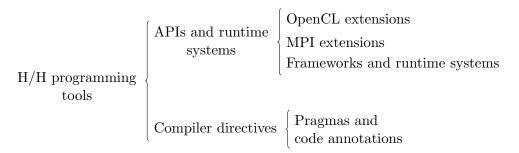

Finally some works proposed new APIs and compiler tools to address the programming problem pointed out above [Augonnet et al., 2011], [Vasudevan et al., 2013], [Elangovan et al., 2014], [Scogland et al., 2014]. The related works can be broadly classified based on the programming tools implemented in the proposal as is depicted in the Fig. 3.1. The details of each proposal are reviewed in the rest of this chapter.

## 3.1 Extensions to OpenCL

OpenCL (Open Computing Language) is a multivendor open standard for generalpurpose parallel programming of heterogeneous systems that includes CPUs, GPUs and

**Figure 3.1:** A classification of the proposals in the state of the art based on the programming tools implemented by each work.

other processors first released in 2009<sup>2</sup>.

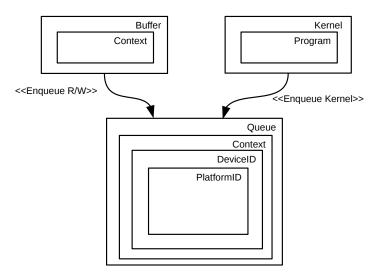

The OpenCL API provides a standard mechanism for offloading portions of the computation over multiple heterogeneous computing devices. This is achieved using a set of handlers mapping the requests of the application to the OpenCL implementations regardless of the architecture of the device.

A typical application in OpenCL is composed by two kinds of code: host code and device code. The former includes all the API function calls to create the handlers, and the latter is code designed to harness data parallelism in the device.

The host code must follow the OpenCL specification that is defined in four parts:

**Platform Model:** Defines the abstract hardware model called "Compute Device", composed of "Compute Units with" (stream multiprocessors) having "Processing Elements (cores)"

**Execution Model:** Defines how the OpenCL environment is configured. Includes concepts like work group, work item, context objects etc.

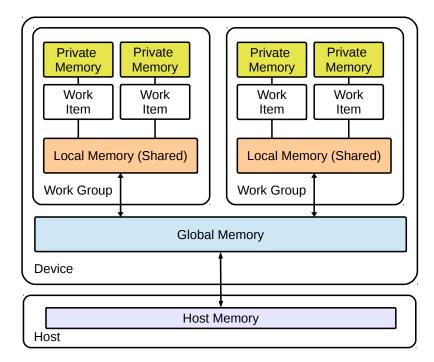

**Memory Model:** Defines the abstract memory hierarchy that kernels use, regardless of the actual underlying memory architecture. The memory model closely resembles current GPU memory hierarchies and is depicted in the Figure: 3.2.

**Programming model:** Defines how the concurrency is mapped to physical hardware. OpenCL supports data parallel and task parallel programming models.

In spite of its advantages OpenCL has two strong disadvantages: The implementations are not interoperable, and it is not designed to scale beyond a single node. This occurs

$<sup>^2{\</sup>rm The~Khronos~Group~(Ed.)}$  (2009, October). The OpenCL specification. Retrieved September 18, 2016, from https://www.khronos.org/registry/cl/specs/opencl-1.0.pdf Version 1.0

Figure 3.2: OpenCL memory model.

due to the fact that neither intercontext nor internode communications are part of the specification.

Some works found in the literature try to overcome those limitations with the aggregation of new functions to the standard API, as well as the implementation of runtime systems that can provide communication services required for internode data transfers or to request kernel executions on remote nodes.

The libWater library [Grasso et al., 2014] implements an event driven task programming model where the runtime system tracks dependency information to dynamically built a list of commands distributed to multiple local command queues. This approach enables the detection of the communication pattern to reduce the number of device-host-device data transfers. This library implements a device query language (DQL) used to ease the mapping of tasks to the computing device that meets some requirements. Although this approach eases considerably the management of computing devices the criteria used for the selection of the device is limited to the information provided by the driver of each device leaving aside another important features like, the compute capability, the internal and external bandwidth, or the latency between computing devices that undoubtedly have a major impact in the performance of the application.

In other works like dOpenCL [Kegel et al., 2012], Hybrid OpenCL [Aoki et al., 2010], and SnuCL [Kim et al., 2012] the key idea is to merge the native OpenCL implementations in the nodes of a distributed system into a single meta platform of OpenCL, and their

implementation is built on top of a middleware that provide communications and eases the synchronization.

In dOpenCL [Kegel et al., 2012] is it possible to execute legacy OpenCL applications with minimal modifications to the source code. A major drawback of this approach is that implies an explicit management of all the devices in the system as well as manual balancing of the workload limiting the scalability and portability of the applications.

Hybrid OpenCL [Aoki et al., 2010] consists of a runtime system that provides an abstraction for different OpenCL implementations and a bridge program to connect the multiple OpenCL implementations over the network. In this work, the communication layer is implemented using sockets instead of the standard MPI middleware however, the employment of sockets can become too complex for large scale systems where the execution of collective operations must be as efficient as possible.

SnuCL [Kim et al., 2012] wants to provide a single system image for heterogeneous CPU/GPU clusters under the idea of a unified operating system with many devices attached to it. The API extensions and the runtime system provide collective communications and event synchronization services through a virtual shared memory approach. In spite of its advantages, the use of a centralized control to handle synchronization and messaging may lead to performance degradation for large scale clusters due to the intensive messaging between the compute nodes and the central control host. Another disadvantage is that this work lacks of scheduling algorithms delegating this complex issue to the programmer.

Sun [Sun et al., 2012] presented an extension to the OpenCL API with a set of functions designed to schedule computing tasks over CPUs and GPUs using pools of tasks. The scheduler employs a fixed policy and event dependencies to determine the next task to be executed. The selection of the device is delegated to the programmer and does not integrates any middleware for inter node communications limiting the scalability of the applications to only one node.

The clOpenCL [Alves et al., 2013] work is based on wrapper libraries with multiple daemons running on each node. The daemons are responsible for the management of its devices, and can redirect the execution of some tasks to other daemons in the cluster. The communication layer is built on top of Open-MX, a high-performance implementation of the Myrinet Express message-passing stack [Goglin, 2008]. This work do not integrates any scheduling tool forcing the programmer to register the devices on the daemons and to select which device must run the tasks.

In clMPI [Takizawa et al., 2013] the key idea is to provide wrapper libraries to ease the interchange of data between multiple GPUs located in different nodes. This work

employs advanced memory strategies like pinned memory allocations or pipelined communications to improve the performance of the applications, and avoids the coordination of blocking and non-blocking MPI calls to the programmer. In spite of the importance of performing efficient data transfers another important issues like task scheduling or device management are not addressed in this work.

The major disadvantages of the works implementing OpenCL extensions are:

- 1. Requires the use of APIs with overwhelming amounts of functions and full understanding of the OpenCL semantics.

- 2. Hiding the MPI interface might in turn limit the scalability of the applications because also hides other MPI functions like, distributed file sharing, one sided communications and collective routines which are fundamental for solving problems having big data sets.

#### 3.2 Extensions to MPI

MPI (the Message Passing Interface) is a open standard for writing message passing programs based on the SPMD (Single Program Multiple Data) paradigm. MPI is considered as the de facto standard for distributed memory programming, and the 1.0 specification was first released in May 1994 <sup>3</sup> and included the definition of the basic terms for massage programming: point-to-point communications, collective operations, process groups, communication contexts, processes topologies, among others. A major update was presented in the second release of the specification in July 1997 that included dynamic process creation and management, one-sided communications, extended collective communications, external interfaces and parallel I/O.

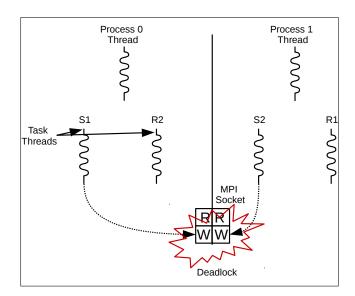

In spite of their remarkable advantages two major concerns: thread safety and heterogeneous computing device integration. Although the MPI API was designed to be thread safe not all implementations can deal with multithreading requests. Aside of this the MPI specification don not includes any mechanism to cope with heterogeneous devices nor with their memory spaces thus requiring additional tools to complete the data transfers.

Some works found in the literature try to overcome the limitations of MPI extending its capabilities to be aware of memory objects located in heterogeneous devices. This is a promising approach given that the MPI semantics fits naturally into other

$<sup>^3</sup>$ Message Passing Interface Forum (Ed.) (1994, May). MPI: A Message-Passing Interface Standard. Retrieved September 18, 2016, from http://mpi-forum.org/docs/mpi-1.0/mpi-10.ps Version 1.0

non-distributed memory fields for example, in shared memory multicore processors, or computers with NUMA architecture.

In cudaMPI [Lawlor, 2009] as well as in many other CUDA-aware implementations of MPI like Open MPI, or MPICH2, the key idea is to provide the tools to achieve an efficient but transparent interchange of data between multiple GPUs. This kind of tools can exploit the advantages of high end network interfaces like myrinet or infiniband to improve the performance of the data transference as well as advanced memory management strategies like asynchronous copy, pinned memory allocations, etc. In spite of this advantages this kind of extensions do not integrate tools for handling the workload distribution problem and only bring support to exploit NVIDIA GPUs.

MPI-ACC [Aji et al., 2012] is a framework designed to allow end-to-end data transfer in accelerator based systems and is implemented on top of MPICH2. The key idea consists in keeping the MPICH2 runtime system aware of the existence of heterogeneous accelerators using specific function calls for those data transfers involving the participation of a GPU. Even though MPI-ACC provides efficient data transfers, the procedural programming model used there enforces the programmer to be aware of many other issues like device initialization and the scheduling problem.

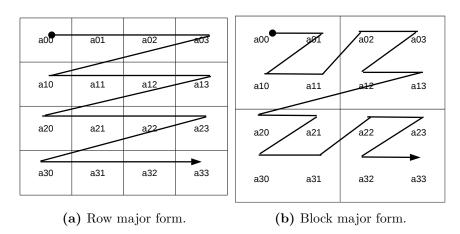

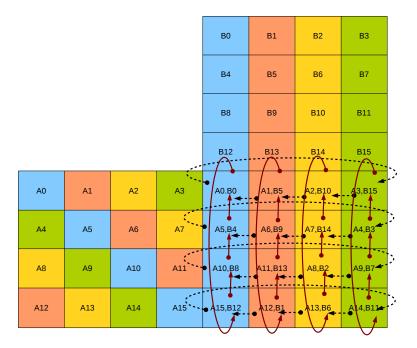

Song [Song and Dongarra, 2012] presented a framework designed to ease the implementation of linear algebra applications where the data can be partitioned in blocks of arbitrary size without compromising the correctness of the algorithm. This framework first defines a static data distribution model based on the type of processing unit (CPU or GPU) and delegates the execution of tasks to the processing units over a specific block of data. The communications required to fulfill the data dependencies between tasks are performed automatically by the framework as well as the assignment of tasks to processing units which is made in order that minimizes the number of data transfers. The major problems with this framework are the assumptions made to perform a fair data distribution, i.e the assumption that all GPUs in the cluster have exactly the same capabilities.

The expectation that the data space can be divided in arbitrary sized and independent blocks is complex even for many applications in linear algebra for example, in matrix multiplication.

In general the current works extending the capabilities of MPI focus on simplify the data transfers between the accelerators but leaving aside other important issues like management and scheduling problem when dealing with multiple heterogeneous accelerators.

#### 3.3 Compiler Directives and Code Annotations

The use of compiler directives (pragmas) and code annotations represent an important direction to ease programming and to perform code analysis prior to the execution of the applications. This approach represents an important alternative to solve the scheduling problem minimizing the data transfers.

The OmpSs+OpenCL proposal [Elangovan et al., 2014] is a task-based programming model that provides portability and flexibility for sequential codes while the performance is improved by the dynamic exploitation of task level parallelism. Tasks in OmpSs are annotated with data direction clauses that specify the data used by the tasks and how it will be used. This work is suitable for programming heterogeneous multi-core and many core architectures but lacks of a middleware to harness distributed systems.

CoreTSAR [Scogland et al., 2014] is a set of OpenMP extensions and libraries for offloading loops and multithread computations to heterogeneous computing devices. This work provides services to ensure memory consistency, task association, and task scheduling. The distribution of data and tasks is described using "pragmas" however, as in other works of this kind the framework it requires a fixed and relatively simple pattern of memory accesses by each thread, and a fixed number of tasks.

In spite of the advantages of those works none integrates a middleware to perform inter node communication or synchronization thus limiting the scope of the applications to a single node.

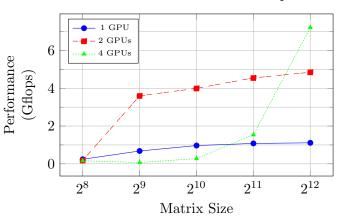

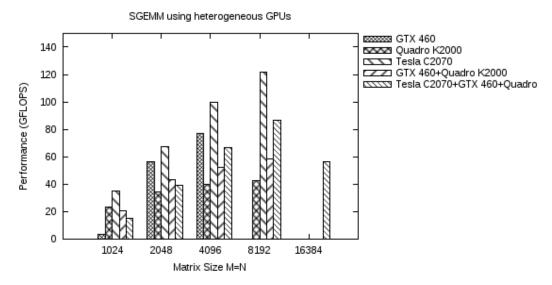

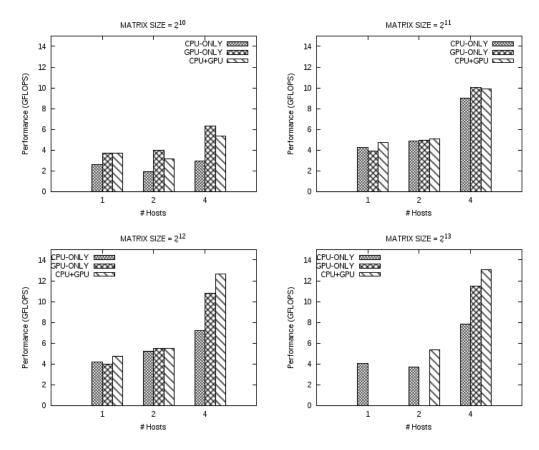

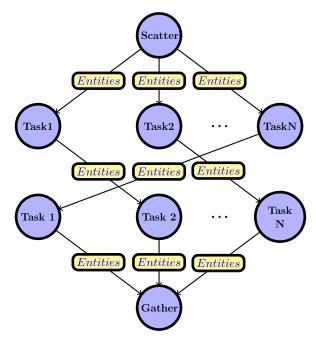

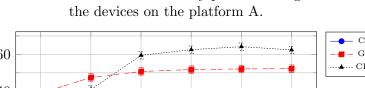

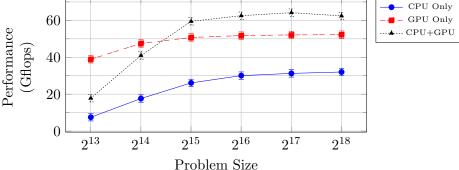

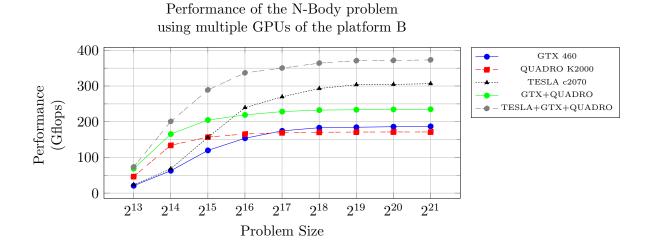

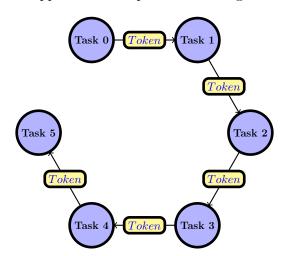

#### 3.4 Frameworks