# UNIDAD ZACATENCO DEPARTAMENTO DE COMPUTACIÓN

### Una Interfaz Generica para Proteger Datos en Memorias USB

Tesis que presenta

Marco Antonio Soto Hernández

Para Obtener el Grado de

Maestro en Ciencias

En Computación

Director de la Tesis:

Dr. Debrup Chakraborty

México, D.F.

Febrero, 2014

# UNIDAD ZACATENCO DEPARTAMENTO DE COMPUTACIÓN

# A Generic Interface for Securing Data in USB Memories

by

Marco Antonio Soto Hernández

Thesis Advisor:

Dr. Debrup Chakraborty

México, D.F.

Febrero, 2014

## Abstract

Portable computing devices have increased a lot both in numbers and varieties in the past few years. These devices provides the convenience of performing several tasks even when the user in "on the go". This mobility has also given rise to new issues in data security. In this thesis we focus on the security of portable memory devices, which are ubiquitous. Because of their small size and portability, there is a high risk of them getting lost, which means the stored data gets compromised.

There are encryption enabled memory devices, which are already available in the market. In these devices, the encryption facility comes along with the specific memory, and thus, such memories are more expensive. Here we plan the solution through a different approach: we aim to design a generic device, which would be capable of enabling encryption in *any* USB memory device. This means, the encryption device can be attached to any ordinary USB memory. We call our device as the Middleman, and present its complete design and implementation.

MiddleMan acts as an interface between a USB memory and a host computer. Externally, it has two USB ports; a host computer and an USB memory can be attached to any of these two ports. There is an encryption algorithm built in within MiddleMan. All bulk data transfers from the host to the memory gets encrypted when it goes through the MiddleMan. Transfers from the memory to the host gets decrypted. This ensures that the data stored in the memory is always encrypted. Internally, the MiddleMan has a functionality of both as an USB device and also as a host. To the memory device, it poses itself as a host, and in turn to the host, it poses like a device, this enables transparent communication to the user of the USB memory. MiddleMan uses a low cost tweakable enciphering scheme as the encryption algorithm, thus it guarantees stronger security than most commercially available encryption enabled USB memories.

This work also includes a prototype implementation of the MiddleMan. As a proof of concept, we implement the full functionality of the MiddleMan in a Spartan 3E FPGA board. For the purpose of this implementation, we also required to enhance the USB support provided by the board. To do this we designed a special extension for the Spartan 3E board, which we call S3USB. This device extends the functionality of the bare board in several respects and can be of independent interest.

We tested the prototype in various computing platforms and found it to work satisfactorily. We also did some controlled performance tests and found it to be efficient. The slowdown that take place in the MiddleMan is within acceptable limits in a typical usage scenario.

## Resumen

Los dispositivos de cómputo pórtatil se han incrementado mucho en cuanto a número y variedad desde hace algunos años. Estos dispositivos nos ofrecen una forma conveniente de realizar varias tareas incluso cuando el usuario va "sobre la marcha". Esta mobilidad tambien ha generado un incremento las cuestiones referentes a la seguridad de datos. En esta tesis nos enfocamos en la seguridad de los dispositivos de memoria portátiles, los cuales son ubicuos. Debido a su pequeño tamaño y portabilidad, existe in alto riezgo de que se extravíen, lo que significa que los datos almacenados son comprometidos.

Existen dispositivos de memoria con capacidades de cifrado, los cuales se encuentran disponibles en el mercado. En estos dispositivos, el cifrado se encuentra adentro del dispositivo, lo cual incrementa su costo. Aquí hemos planeado una solución por medio de un enfoque diferente: nosotros nos concentramos en el diseño de un dispositivo genérico, el cual pueda ser capaz de cifrar cualquier memoria USB. Nosotros hemos llamado a este dispositivo MiddleMan, además presentamos su completo diseño e implementación.

MiddleMan actúa como una interface entre una memoria USB y una computadora huésped. Posee dos puertos externos; una computadora huésped y una memoria USB pueden ser conectados a cualquiera de estos dos puertos. Existe un algoritmo de cifrado implementado dentro de MiddleMan. Todas las transferencias en masa desde el huésped hasta la memoria son cifradas a travez de MiddleMan. Transferencias de la memoria al huésped son descifradas. Esto nos asegura que los datos almacenados en la memoria siempre permanezcan cifrados. Internamente, MiddleMan funciona como un dispositivo USB y también como un huésped. Ante el dispositivo de memoria, este se presenta como un host, mientras que para el huésped, se presenta como un dispositivo, esto logra comunicaciones transparentes para el usuario de la memoria USB. MiddleMan utiliza un esquema de cifrado ajustable como su algoritmo de cifrado y por lo tanto, garantiza una seguridad más fuerte que las soluciones comerciales.

Este trabajo también incluye una implementación prototipo de MiddleMan. Como prueba de concepto, hemos implementado todas las funcionalidades de MiddleMan en una tarjeta FPGA Spartan 3E. Para propósitos de esta implementación, también requerimos de una mejora en el soporte USB de la Spartan 3E. Para esto diseñamos una extensión especial para dicha tarjeta y la llamamos S3USB. Esta extensión incrementa la funcionalidad de la tarjeta FPGA en varios aspectos y este diseño es de interés por si solo.

Hemos probado el prototipo en varias plataformas de cómputo y encontramos que funciona satisfactoriamente. También hemos hecho algunas pruebas de rendimiento controladas y encontramos que es efficiente. El alentamiento que toma lugar dentro de MiddleMan, se encuentra dentro de los límites aceptables para un escenario de uso típico.

# Contents

| Li            | List of Figures x      |                                            |    |  |  |  |  |

|---------------|------------------------|--------------------------------------------|----|--|--|--|--|

| $\mathbf{Li}$ | st of                  | Tables                                     | xv |  |  |  |  |

| 1             | Intr                   | oduction                                   | 1  |  |  |  |  |

|               | 1.1                    | Storage Security and the MiddleMan         | 2  |  |  |  |  |

|               | 1.2                    | The Organization of the Thesis             | 5  |  |  |  |  |

| 2             | Secure Storage of Data |                                            |    |  |  |  |  |

|               | 2.1                    | Notations                                  | 7  |  |  |  |  |

|               | 2.2                    | Storage Encryption                         | 8  |  |  |  |  |

|               | 2.3                    | Tweakable Enciphering Schemes              | 8  |  |  |  |  |

|               | 2.4                    | STES Construction                          | 10 |  |  |  |  |

|               | 2.5                    | Implementation of STES                     | 10 |  |  |  |  |

| 3             | The                    | Universal Serial Bus                       | 15 |  |  |  |  |

|               | 3.1                    | USB Basics                                 | 15 |  |  |  |  |

|               |                        | 3.1.1 Components of the bus                | 15 |  |  |  |  |

|               |                        | 3.1.2 USB Supported Speeds                 | 17 |  |  |  |  |

|               | 3.2                    | The Physical Layer                         | 18 |  |  |  |  |

|               | 3.3                    | Serial Interface Engine                    | 19 |  |  |  |  |

|               | 3.4                    | Endpoints                                  | 19 |  |  |  |  |

|               | 3.5                    | Protocol                                   | 20 |  |  |  |  |

|               |                        | 3.5.1 Transactions                         | 20 |  |  |  |  |

|               |                        | 3.5.2 Packet Structure                     | 21 |  |  |  |  |

|               | 3.6                    | Transfer Types                             | 23 |  |  |  |  |

|               | 3.7                    | USB Device Classes                         | 24 |  |  |  |  |

|               |                        | 3.7.1 USB Mass Storage Class               | 25 |  |  |  |  |

|               | 3.8                    | USB Storage Architecture                   | 25 |  |  |  |  |

| 4             | Design Overview        |                                            |    |  |  |  |  |

|               | 4.1                    | Design Goals and Decisions                 | 27 |  |  |  |  |

|               | 4.2                    | Design of the MiddleMan                    | 29 |  |  |  |  |

|               |                        | 4.2.1 Functionality of a USB Memory Device | 29 |  |  |  |  |

$\mathbf{x}$  CONTENTS

|              | 4.3<br>4.4<br>4.5 | 4.2.3 Design Options for MiddleMan      | 29<br>32<br>34<br>35<br>37 |  |  |  |  |  |  |

|--------------|-------------------|-----------------------------------------|----------------------------|--|--|--|--|--|--|

|              | 4.6               |                                         | 38                         |  |  |  |  |  |  |

| 5            | Har               | dware Design                            | 11                         |  |  |  |  |  |  |

|              | 5.1               | Design Considerations                   | 41                         |  |  |  |  |  |  |

|              | 5.2               | Spartan 3E Connectivity                 | 42                         |  |  |  |  |  |  |

|              | 5.3               | Design of the S3USB Expansion Board     | 44                         |  |  |  |  |  |  |

|              |                   | 5.3.1 S3USB circuit functionality       | 44                         |  |  |  |  |  |  |

|              | 5.4               |                                         | 46                         |  |  |  |  |  |  |

|              | 5.5               |                                         | 49                         |  |  |  |  |  |  |

|              | 5.6               |                                         | 51                         |  |  |  |  |  |  |

| 6            | Rec               | configurable USB Architecture 53        |                            |  |  |  |  |  |  |

| •            | 6.1               | 0                                       | 53                         |  |  |  |  |  |  |

|              | 6.2               |                                         | 55                         |  |  |  |  |  |  |

|              | 0.2               | · ·                                     | 55                         |  |  |  |  |  |  |

|              |                   |                                         | 59                         |  |  |  |  |  |  |

|              | 6.3               |                                         | 32                         |  |  |  |  |  |  |

|              | 0.0               |                                         | 33                         |  |  |  |  |  |  |

|              |                   |                                         | 35                         |  |  |  |  |  |  |

|              |                   |                                         | 38                         |  |  |  |  |  |  |

| 7            | Test              | ts and Performance Results              | 31                         |  |  |  |  |  |  |

| •            | 7.1               |                                         | 31                         |  |  |  |  |  |  |

|              | 7.2               | 9                                       | 32                         |  |  |  |  |  |  |

| 8            | Con               | aclusion and Future Work                | 35                         |  |  |  |  |  |  |

|              | 8.1               |                                         | 35                         |  |  |  |  |  |  |

|              | 8.2               | ē ·                                     | 38                         |  |  |  |  |  |  |

| $\mathbf{A}$ | USI               | B Suplementary Information              | )1                         |  |  |  |  |  |  |

|              |                   | - · · · · · · · · · · · · · · · · · · · | 91                         |  |  |  |  |  |  |

|              |                   |                                         | ว 1                        |  |  |  |  |  |  |

# List of Figures

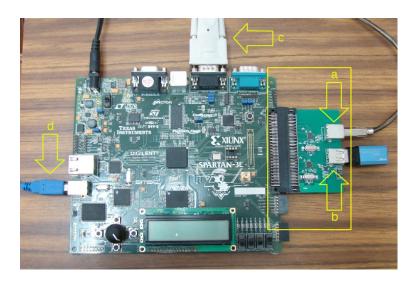

| 1.1 | The prototype of the MiddleMan. The yellow rectangle marks the hardware extension S3USB that we attached with the Spartan 3E board for implementing the physical layer. <b>a</b> ) Device USB port, <b>b</b> ) Host USB port, <b>c</b> ) Serial port for debugging, <b>d</b> ) FPGA configuration port                                                                                                                                             | ۷        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1 | STES: A TES using SC and MLUH. The $\ell$ -bit string fStr is a parameter to the whole construction. The length of the IV of SC is $\ell$ and the data                                                                                                                                                                                                                                                                                             | -1 -     |

| 2.2 | path of MLUH is $d$ . This figure has been taken verbatim from [10] The Feistel network (and its inverse) constructed using a stream cipher and a MLUH. The variable $\ell$ is the length of an IV for SC and $d$ is the data path of MLUH. This definition is different from the usual Feistel construction: a positive integer $i$ is provided as an additional input and a binary string $W$ of length $i$ is returned as an additional output. | 1:       |

| 2.3 | This figure has been taken verbatim from [10]                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>13 |

| ۷.5 | Architecture of STES                                                                                                                                                                                                                                                                                                                                                                                                                               | 10       |

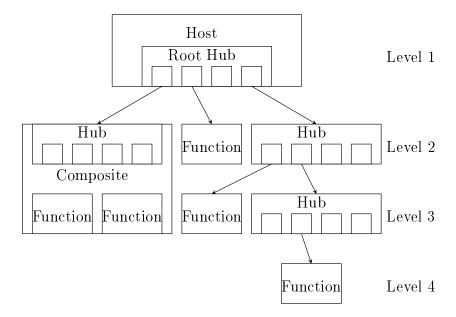

| 3.1 | USB topology                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16       |

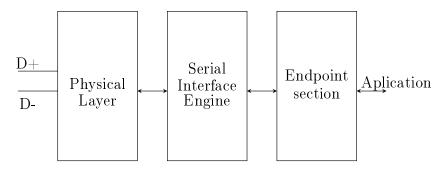

| 3.2 | USB device components                                                                                                                                                                                                                                                                                                                                                                                                                              | 17       |

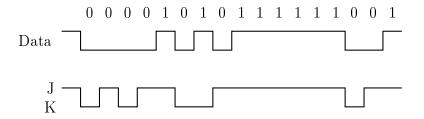

| 3.3 | NRZI encoding                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19       |

| 3.4 | Stages of a transaction                                                                                                                                                                                                                                                                                                                                                                                                                            | 2        |

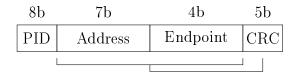

| 3.5 | Fields inside a token packet                                                                                                                                                                                                                                                                                                                                                                                                                       | 2        |

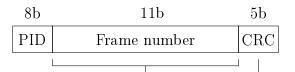

| 3.6 | Fields inside a SOF packet                                                                                                                                                                                                                                                                                                                                                                                                                         | 22       |

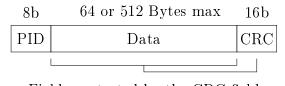

| 3.7 | Fields inside a data packet                                                                                                                                                                                                                                                                                                                                                                                                                        | 23       |

| 3.8 | Stages of a control transfer                                                                                                                                                                                                                                                                                                                                                                                                                       | 2        |

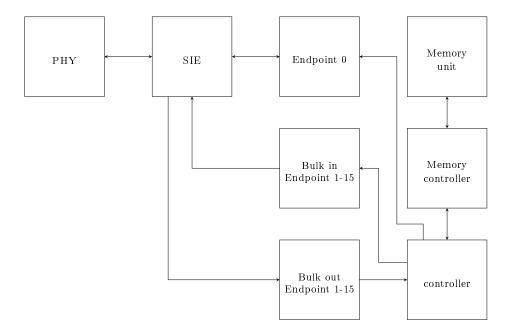

| 3.9 | A common USB memory architecture                                                                                                                                                                                                                                                                                                                                                                                                                   | 25       |

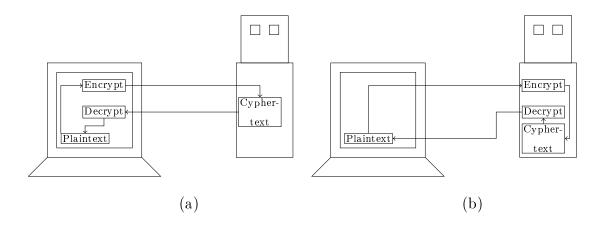

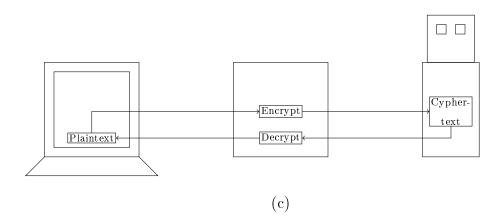

| 4.1 | USB memory encryption methods: a) Within the PC, b) In the USB controller, c) In an external device                                                                                                                                                                                                                                                                                                                                                | 28       |

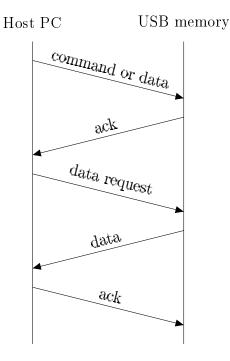

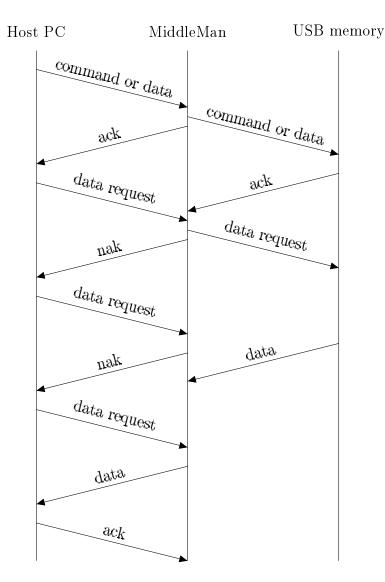

| 4.2 | USB communications data flow                                                                                                                                                                                                                                                                                                                                                                                                                       | 30       |

| 4.3 | USB communications data flow with MiddleMan                                                                                                                                                                                                                                                                                                                                                                                                        | 3        |

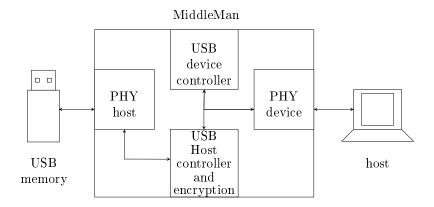

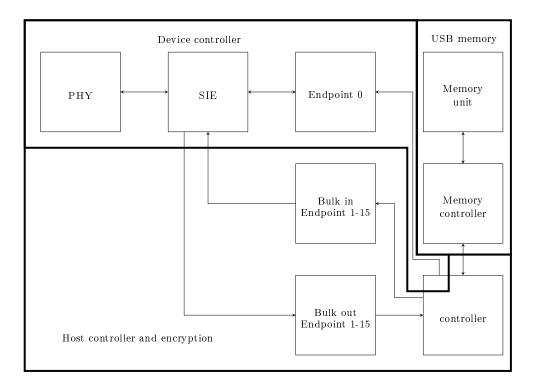

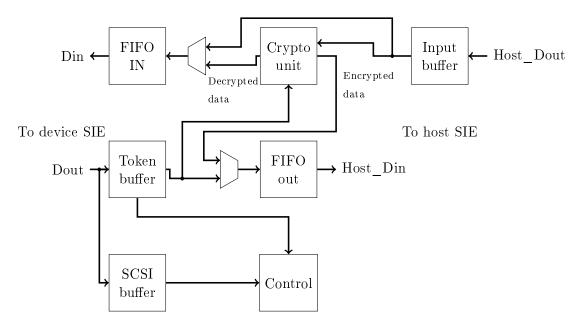

| 4.4 | Components inside the MiddleMan implementation                                                                                                                                                                                                                                                                                                                                                                                                     | 32       |

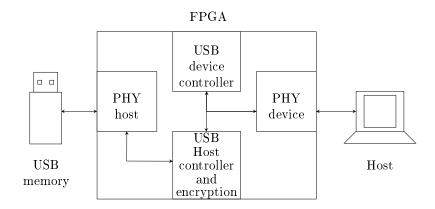

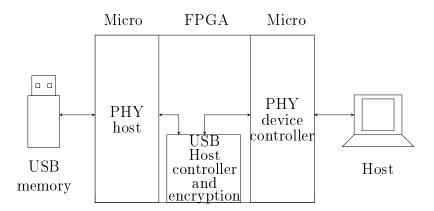

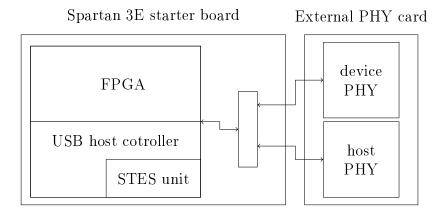

| 4.5 | FPGA implementation                                                                                                                                                                                                                                                                                                                                                                                                                                | 33       |

| 4.6 | FPGA + microcontroller implementation                                                                                                                                                                                                                                                                                                                                                                                                              | 33       |

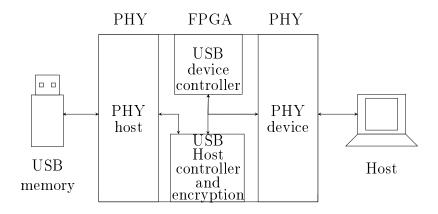

| 4.7 | FPGA + physical layer implementation                                                                                                                                                                                                                                                                                                                                                                                                               | 34       |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

xii LIST OF FIGURES

| 4.8  | FPGA + physical layer external card                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.9  | Location of the protocol implementation                                                                                                                                                                   |

| 4.10 | Location of the encryption implementation                                                                                                                                                                 |

| 4.11 | Common USB architecture with MiddleMan's block division                                                                                                                                                   |

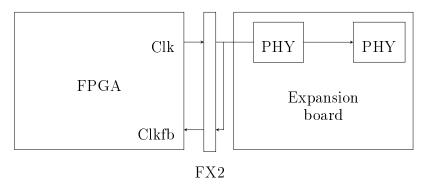

| 5.1  | FPGA clock sourcing                                                                                                                                                                                       |

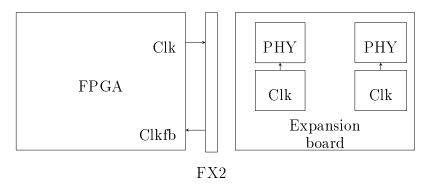

| 5.2  | External clock sourcing                                                                                                                                                                                   |

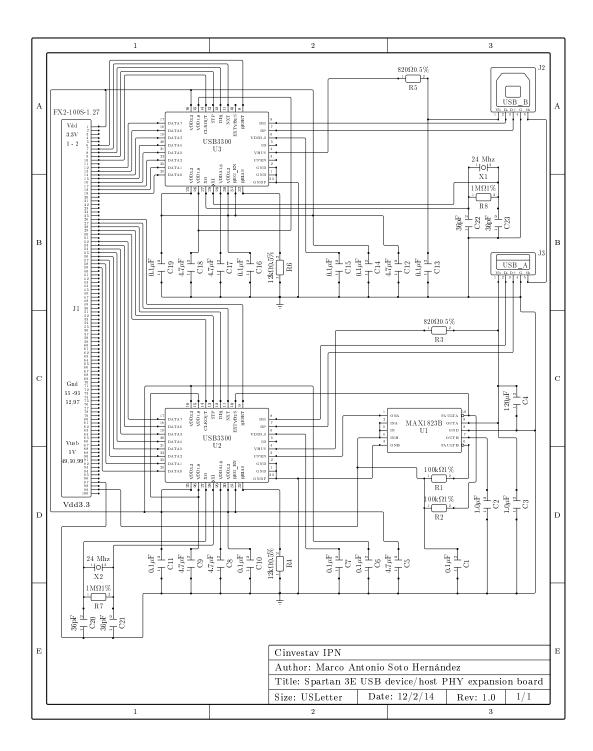

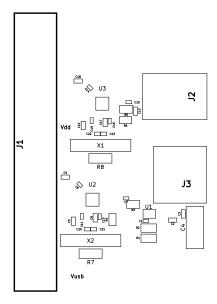

| 5.3  | PHY schematic                                                                                                                                                                                             |

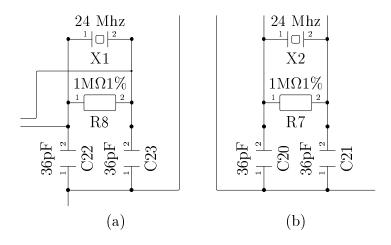

| 5.4  | Close up of the oscillator networks of Figure 5.3. a) Device block oscillator, b) Host block oscillator. Pins 1 and 2 of components X1 and X2 connect directly to pins XO and XI of components U2 and U3. |

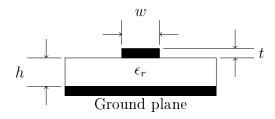

| 5.5  | Micro strip parameters diagram                                                                                                                                                                            |

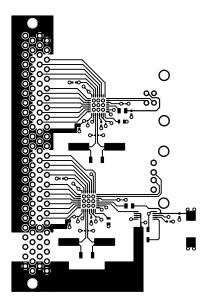

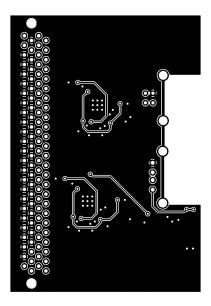

| 5.6  | S3USB Front PCB layer (signal layer)                                                                                                                                                                      |

| 5.7  | S3USB back PCB layer (ground and power layer)                                                                                                                                                             |

| 5.8  | S3USB silk screen layer (component labels)                                                                                                                                                                |

| 5.9  | The S3USB expansion board.                                                                                                                                                                                |

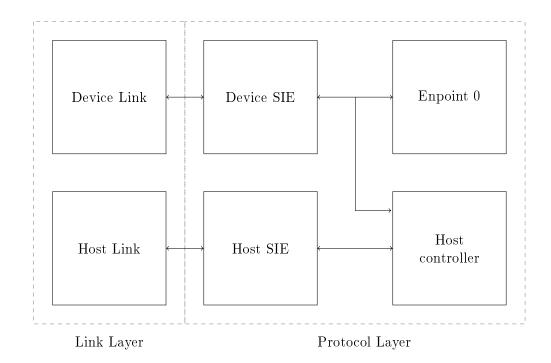

| 6.1  | Block diagram of the UPRC architecture                                                                                                                                                                    |

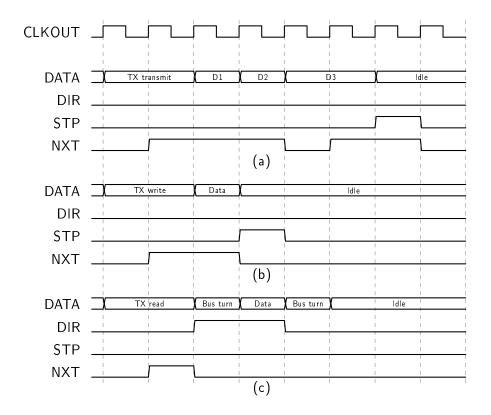

| 6.2  | TX commands. a) Transmit command, b) Write command and c)Read command                                                                                                                                     |

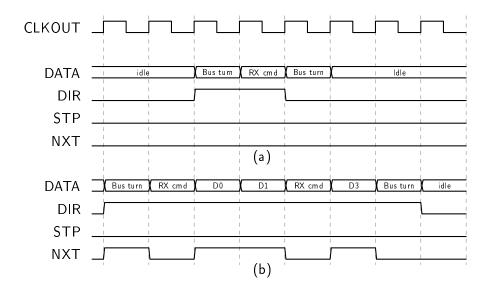

| 6.3  | RX commands. a) RX command with the PHY status, b) RX command for USB packet receptions. RX commands are received between USB data to update the PHY status                                               |

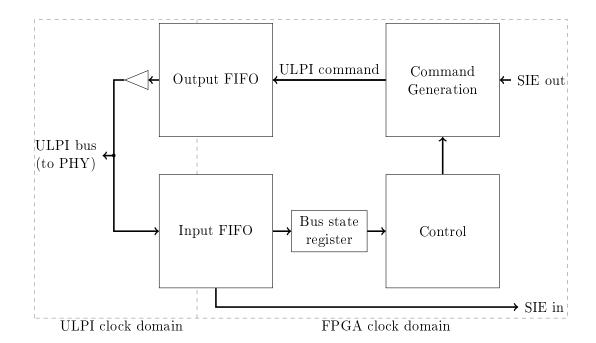

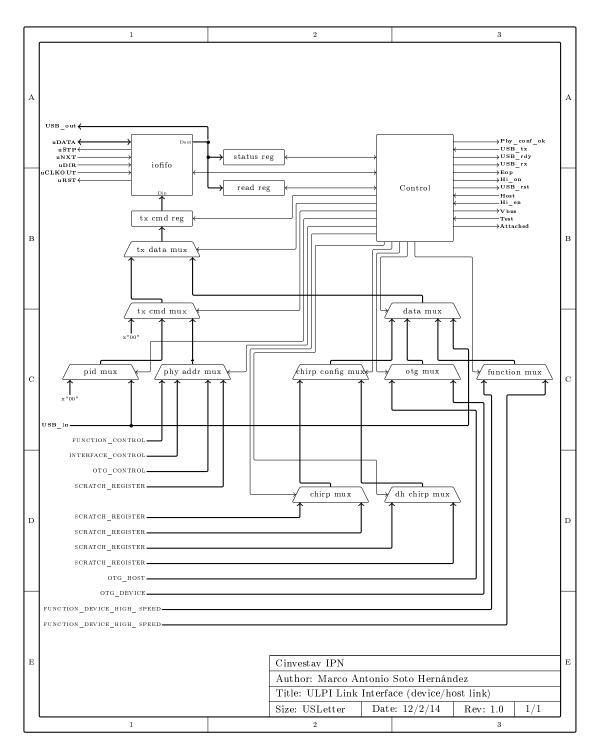

| 6.4  | Block diagram of the ULPI link layer                                                                                                                                                                      |

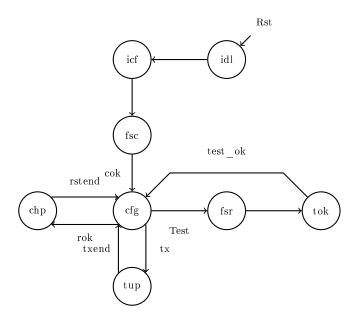

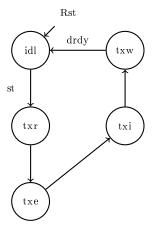

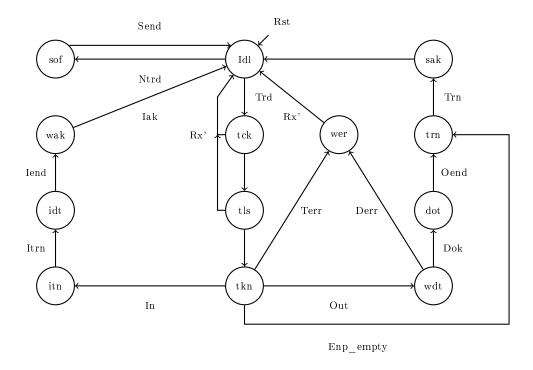

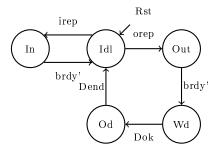

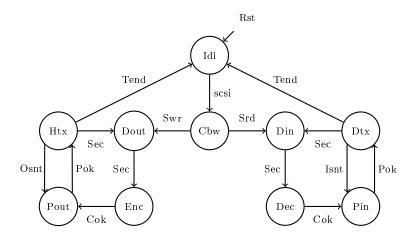

| 6.5  | Link Layer state diagram.                                                                                                                                                                                 |

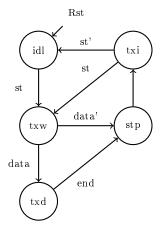

| 6.6  | TX write command FSM                                                                                                                                                                                      |

| 6.7  | TX read command FSM                                                                                                                                                                                       |

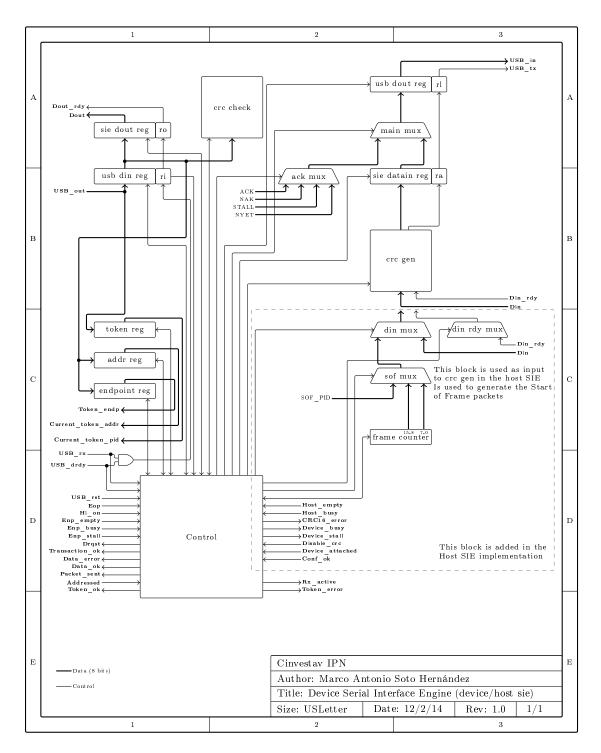

| 6.8  | Serial Interface Engine architecture                                                                                                                                                                      |

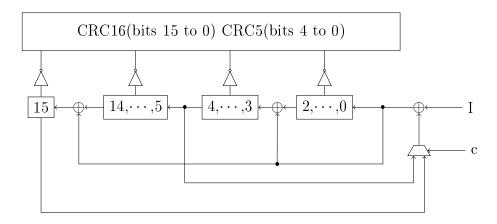

| 6.9  | CRC Generation architecture                                                                                                                                                                               |

| 6.10 |                                                                                                                                                                                                           |

| 6.11 | Serial Interface Engine state diagram                                                                                                                                                                     |

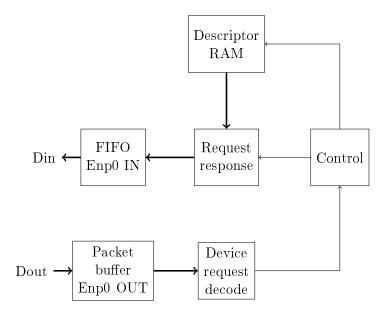

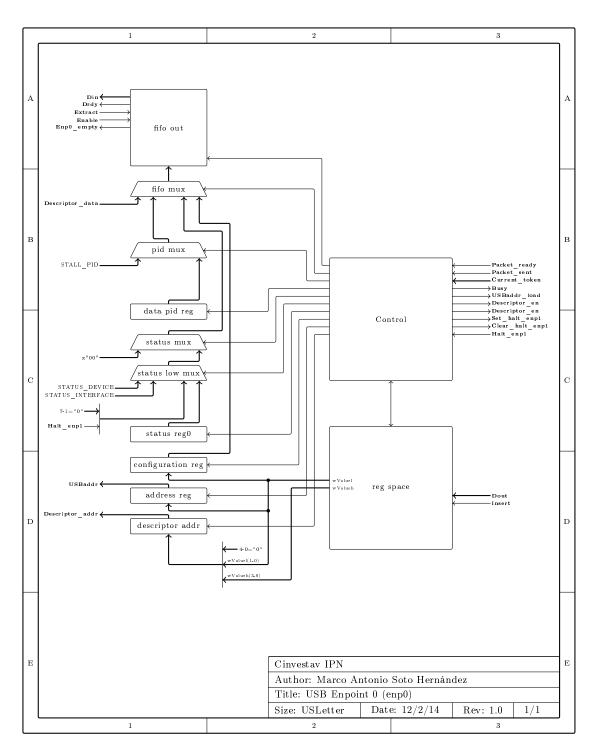

|      | Endpoint 0 architecture                                                                                                                                                                                   |

|      | Endpoint 0 state diagram.                                                                                                                                                                                 |

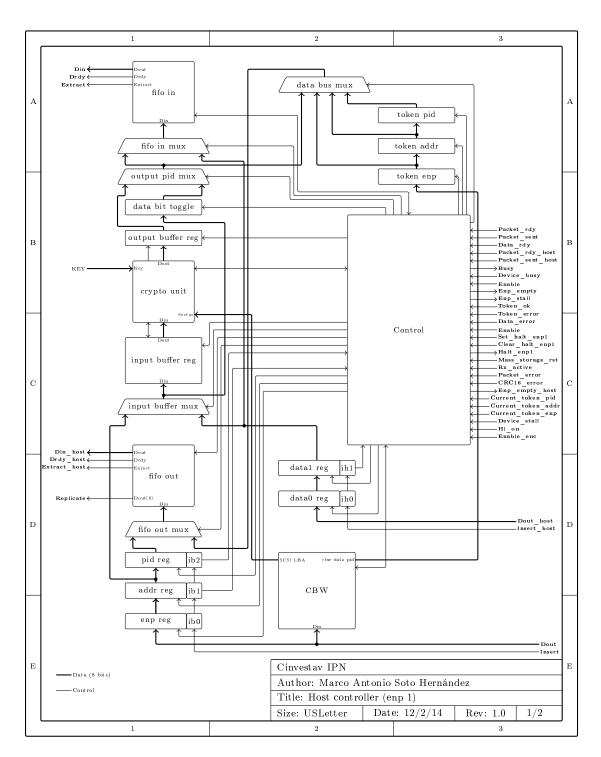

|      | Host controller architecture                                                                                                                                                                              |

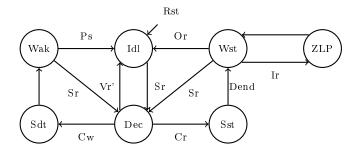

|      | Host controller packet replicator state diagram.                                                                                                                                                          |

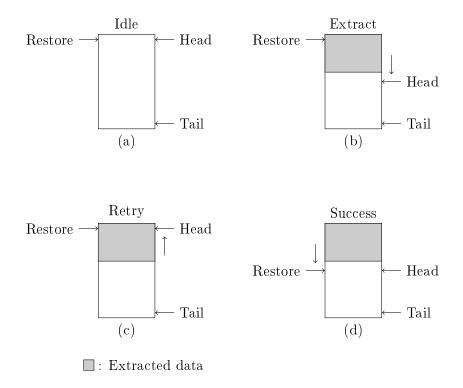

|      | Success Retry FIFO functionality                                                                                                                                                                          |

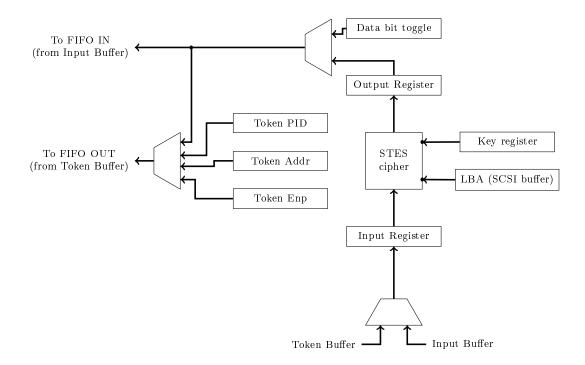

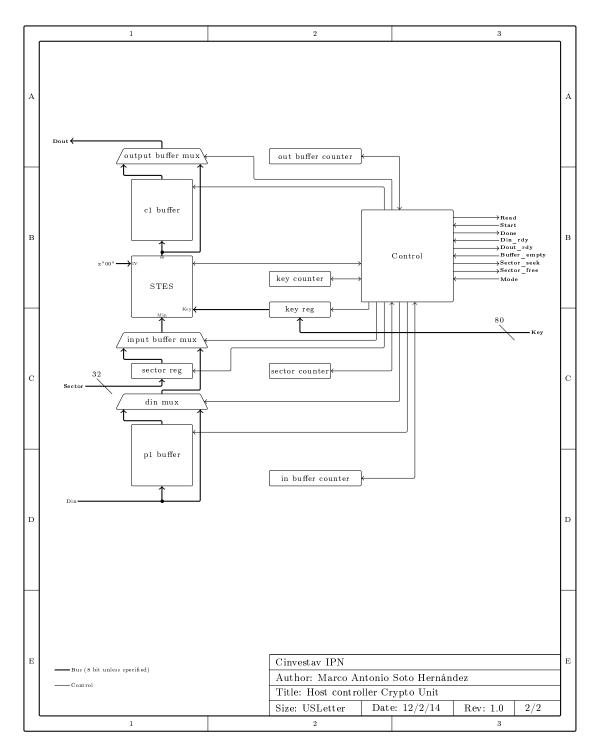

|      | Host controller encryption architecture (Crypto unit)                                                                                                                                                     |

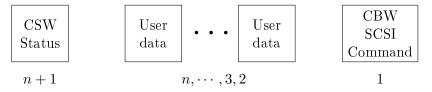

| 0.17 | Packet sequences in a bulk transfer for a SCSI command. Each packet                                                                                                                                       |

| C 10 | is prepended with an IN or OUT token                                                                                                                                                                      |

|      | Endpoint 1 USB bulk, SCSI and Cipher state diagram                                                                                                                                                        |

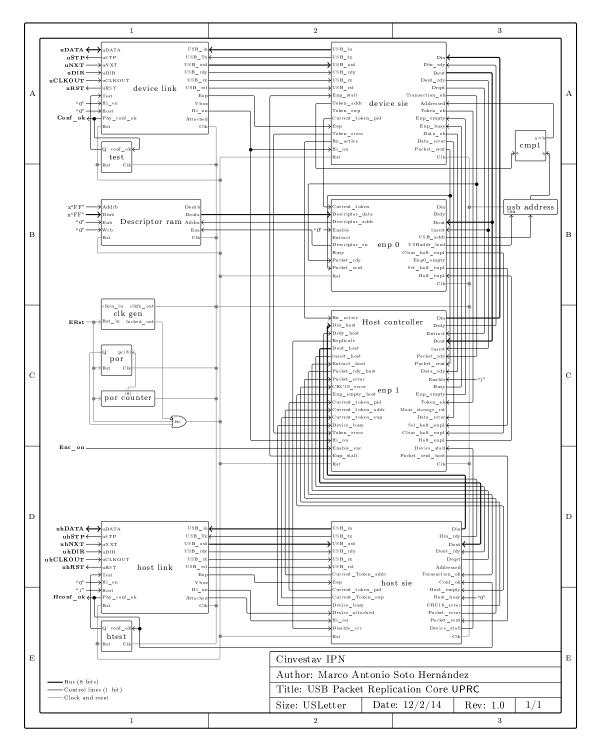

|      | USB Packet Replication Core architecture                                                                                                                                                                  |

|      | ULPI Link Layer architecture                                                                                                                                                                              |

|      | USB device and host Serial Interface Engine architecture                                                                                                                                                  |

|      | Endpoint 0 architecture.                                                                                                                                                                                  |

| 6.23 | Host controller architecture                                                                                                                                                                              |

| LIST OF FIGURES                                 | xiii   |

|-------------------------------------------------|--------|

| 6.24 Host controller's Crypto unit architecture | <br>79 |

| A.1 Architecture of the CRC calculator          | <br>94 |

# List of Tables

| 3.1 | USB speed configurations                                                            | 17 |

|-----|-------------------------------------------------------------------------------------|----|

| 3.2 | USB 2.0 signaling                                                                   | 18 |

| 3.3 | USB Packet IDs                                                                      | 22 |

| 4.1 | Comparison table between encryption methods of Figure 4.1                           | 28 |

| 4.2 | Performance comparison between design options for the $MiddleMan.$ .                | 34 |

| 5.1 | J1 connector pin-out                                                                | 47 |

| 5.2 | USB3300 bus interface signals                                                       | 47 |

| 5.3 | Parameters calculated for the capacitors of Figure 5.4                              | 49 |

| 6.1 | The ULPI bus signals                                                                | 56 |

| 6.2 | S3USB Register space only some registers where omitted                              | 56 |

| 6.3 | TX commands                                                                         | 57 |

| 6.4 | USB required Device requests                                                        | 65 |

| 7.1 | Parameters for the speed test of the MiddleMan                                      | 83 |

| 7.2 | Speed results for the MiddleMan                                                     | 83 |

| 7.3 | Spartan 3E resources used by the MiddleMan unit                                     | 84 |

| A.1 | Device requests data structure. This table was taken from the USB 2.0 specification | 92 |

| A.2 | Device requests needed to perform the enumeration process                           | 92 |

xvi LIST OF TABLES

## Abbreviations

| AES  | Advanced Encryption Standard            |

|------|-----------------------------------------|

| ACK  | Acknowledge in a USB handshake          |

| CBW  | Command Block Wrapper                   |

| CRC  | Cyclic Redundancy Code                  |

| CSW  | Command Status Wrapper                  |

| EEFF | Effective Relative Permittivity         |

| ENPX | Endpoint X, where X is a number         |

| FIFO | Fist IN First Out memory system         |

| FPGA | Field Programmable Gate Array           |

| FSM  | Finite State Machine                    |

| IN   | USB IN transaction                      |

| IP   | Intelectual Property                    |

| MLUH | Multilinear Universal Hash              |

| NAK  | Negative acknowledge in a USB handshake |

| NRZI | Non Return Zero Invert                  |

| OTG  | USB On The Go                           |

| OUT  | USB OUT transaction                     |

| PCB  | Printed Circuit Board                   |

| PHY  | Physical Layer                          |

| PID  | USB Packet Identifier                   |

| RFID | Radio Frequency Identification          |

| SIE  | Serial Interface Engine                 |

| TES  | Tweakable Enciphering Schemes           |

| SOF  | USB Start Of Frame                      |

| UPRC | USB Packet Replication Core             |

| STES | Small TES                               |

| ULPI | UTMI Low Pin Interface                  |

| USB  | Universal Serial Bus                    |

|      |                                         |

USB 2.0 Transceiver Macrocell Interface

UTMI

# Chapter 1

## Introduction

Data storage is an important part in computer systems. There are several ways of storing data, ranging from internal hard drives in desktop/laptop computers to portable flash based storage devices. Even the popular portable digital devices in the market like smart phones, tablets, cameras, etc., have some way to store data. The increase of portable devices and the improvements in their connectivity to the Internet has raised numerous security concerns regarding data stored in various kinds of storage media. The convenience of portability which most devices offer today can also be a problem: the smaller the device, the easier it can be lost.

In the last few years there has been significant activity towards designing cryptographic algorithms suitable for storage security [20, 21, 18, 11, 19, 32, 10], also there have been some standardization efforts [3, 4]. Thus in terms of designing secure and efficient cryptographic algorithms suitable for securing stored data there has been significant improvements. On the other hand, in open literature much is not reported about practical deployments of these algorithms in specific devices. Though, there are commercially available storage devices with encryption facilities, the intricacies of their designs are trade secrets. This prevents easy reproducibility of those designs and also prevents large scale security analysis of such devices.

In this thesis we design a novel device for enabling encryption in an external USB memory. We name the device as MiddleMan. The basic functionality of MilddleMan is to act as a special interface between an USB memory and the host computing system (say a desktop or a laptop computer). MiddleMan is equipped with an encryption algorithm and all bulk data transfers from the computer to the memory are encrypted when passing through the MiddleMan. Transfers from the memory to the computer get decrypted. Thus, the data that resides in the memory is always encrypted. The MiddleMan is neither a part of the USB memory nor the host computing system, thus any USB memory device can be connected to any computer using the device in the middle to obtain functionality of encryption in the memory.

In this thesis we do a careful design of the MiddleMan and also do a prototype implementation of the design in a Spartan 3E FPGA board. We decided to use an FPGA, because it provides high flexibility in terms of low level, fast hardware applications. In addition, the Spartan 3E board also provides a low cost FPGA

solution. We have performed extensive testing with the prototype using different computing environment and we found the device to work satisfactorily.

#### 1.1 Storage Security and the MiddleMan

Bulk storage in modern computing devices is provided through hard disks or NAND type flash memories. Though the technology behind these two options are quite different, they are similar in that both of them are organized as sectors. A sector is the smallest addressable part of these storage systems and the host computing device reads or writes on these medias at sector level granularity.

There exist a rich cryptographic literature which addresses the problem of encrypting sector oriented storage media. Also, there is a consensus in the cryptographic community that a class of encryption algorithms, called tweakable encryption schemes (TES) are best suited for the application [20]. To date there are numerous proposals of TES which are efficient and proven secure in a well accepted and reasonable security model.

The specific application area where TES can be deployed is called "in-place disk encryption". In this application the encryption algorithm is part of the disk/memory controller and it encrypts sectors before it writes to the disk and decrypts sectors before it sends them to the operating system. This model is general and can be applied to any storage media organized into sectors, irrespective of the other high level systems like operating systems, file systems, etc.

There are two relevant active standards which specifies cryptographic algorithms for storage encryption. The IEEE 1619-2007 [3] specifies an algorithm called XTS-AES [30], and the IEEE 1619.2-2010 [4] specifies two algorithms EME2 [21, 18] and XCB [31]. EME2 and XCB are TES<sup>1</sup>. XTS-AES is not a TES, and the security guarantees that XTS-AES provides are much less than those provided by any secure TES, in particular XTS encryption is vulnerable to tampering which any TES can resist to some extent. Security limitations of XTS are widely known and some details regarding this can be found in [2, 17].

The advantage of XTS over any known TES is its efficiency, as it uses far less operations than any known TES and thus when implemented either in software or hardware would be much more efficient both in terms of speed and area compared to any TES. But it is to be noted that there have been extensive studies on implementation of TES both in software [17] and hardware [29, 7, 10, 28] which suggests that a TES when implemented using reasonable resources can exceed the data rates of modern disk/memory controllers. Hence there is no efficiency barrier for the use of TES in the required application, and given that TES are more secure it should be preferred to the XTS algorithm.

<sup>&</sup>lt;sup>1</sup>Recently there was some attacks reported on XCB [9, 22], which questions the so far known security properties of XCB. These observations thus puts into doubt the security of XCB and also the standard which specifies it.

In this work we are interested in encryption of USB memories. To apply in-place disk encryption in case of USB memories, the most suited design strategy would be to implement the encryption algorithm within the memory controller. Thus, the encryption unit would be part of the memory stick. Such products are commercially available [25], for example, Kingston, which is a major player in the market of USB memories, has a spectrum of offerings of secure USB drives [1]. As expected the details of these designs are not publicly available, but they reveal the encryption algorithms that they use. The secure USB drives marketed by Kingston either use XTS (as in Data Traveller Vault Privacy 3.0 and Data Traveller 6000) or CBC (as in Data Traveller Vault Privacy Managed and Data Traveller 4000). It is curious that these commercially available products do not implement any TES, which is known to be the best suited algorithms for this application. The reason behind this is probably both CBC and XTS are much less complex than most known TES. It is to be noted that CBC is a privacy only block cipher mode, which does not provide adequate security for disk encryption and as already discussed, XTS though standardized for disk encryption purposes, cannot match the security levels provided by a secure TES.

The design that we propose in this thesis is different from the commercial products described above. We aim to achieve a generic device for USB memory encryption, which would be independent of both the memory device and the host. Our proposal, the MiddleMan, acts as a encryption interface between any host and any USB bulk storage device. The most important advantage of this philosophy is that we do not require to depend on the USB memory vendor for its security, we can use an encryption algorithm of our choice to encrypt our memory. Moreover, a single encryption device can be used to encrypt multiple memories.

To achieve the above mentioned objective, the MiddleMan has both the functionality of an USB host and a device. In simple terms, the MiddleMan accepts two USB connections, with one it connects to the memory device and with the other it connects to a host (for example a PC). To the memory device, it acts like a host and thus receives bulk data transfers and redirects to the real host. To this real host the MiddleMan posses as an USB device. MiddleMan has an encryption algorithm residing within it: the host to the memory device transfers are encrypted and the transfers from the memory device to the host are decrypted. While encrypting/decrypting the MiddleMan follows the philosophy of in-place disk encryption, i.e., it performs sector wise encryption/decryption of all bulk transfers which passes through it.

The basic design of MiddleMan can support any encryption algorithm. In our implementation we use a specific TES which is called STES [10]. STES is a recent proposal which is very different from existing TES. The difference is that STES was designed with the goal that when implemented suitably, it would have a very small hardware and power footprint. This characteristic of STES is very important when is used in MiddleMan, as this gives us a secure, efficient and low cost encryption algorithm.

The design of MiddleMan was done so that a big part of the design can be implemented within a reconfigurable fabric like a field programmable gate array (FPGA).

Figure 1.1: The prototype of the MiddleMan. The yellow rectangle marks the hardware extension S3USB that we attached with the Spartan 3E board for implementing the physical layer. **a**) Device USB port, **b**) Host USB port, **c**) Serial port for debugging, **d**) FPGA configuration port.

With the advent of small, low power and cheap FPGA families like Spartan, Lattice etc., it may be possible that a practical realization of MiddleMan has an FPGA in it. This would enable reconfigurability, then at least the built-in encryption algorithm may be suitably changed according to diverse security needs or local security legislation. Thus, MiddleMan provides a highly flexible and generic way to implement in place encryption in a variety of USB mass storage devices, which can be practically useful. Moreover, to the best of our knowledge there does not exist a device or a design which is even similar to the design philosophy and goals of the MiddleMan.

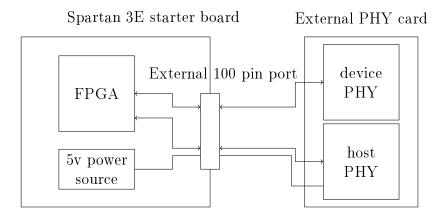

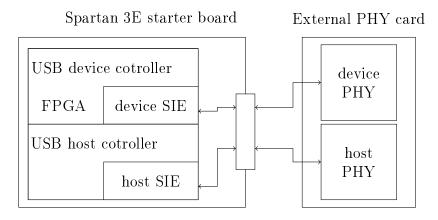

This thesis also includes a prototypical implementation of most functionalities of MiddleMan. The implementation was done in a Spartan 3E starter board. This board is equipped with some rudimentary USB facilities, but these were not enough for our purpose. Thus, we needed to extend the board with some custom designed hardware where we implement the USB physical layer. We call this special add on to the board as S3USB. This extended board can be of independent interest, and can serve as a test platform for prototypical implementations of other applications, which uses the USB protocol.

To achieve the intended functionality, we had to implement the whole USB protocol from scratch in an FPGA. There exist some open FPGA cores [27, 36], but we found them to be in sufficient for our purpose. In our design, we implement the full device USB protocol and additionally implement the part of the host protocol, which is required for our design. Finally we suitably aggregate an FPGA implementation of STES in our design to obtain the full functionality of MiddleMan.

The final prototype that we developed is shown in Figure 1.1. As is clear from the figure, for implementing the prototype we had to extend the Spartan 3E board by a

custom built circuit, the S3USB (marked by a yellow rectangle in the figure). The device and host USB ports (marked a and b respectively in the figure) are parts of S3USB. For using the device one needs to insert a USB memory in port b and connect it to the host (a PC, laptop, tablet etc.) through port a. Once such a connection is made, all data written to the USB memory by the host gets encrypted and any data read by the host from the USB memory gets decrypted by the MiddleMan. For enabling encryption functionality in any USB memory, the memory needs to be formatted after it is connected to the host through the MiddleMan. This ensures that the boot sector and the partition table in the memory are also encrypted. Thus if it is connected to any host without the MiddleMan, the host will not recognize the data inside the USB memory<sup>2</sup>. But when connected with the MiddleMan the host receives the data in a decrypted form, and thus usual functionality of an USB memory resumes.

As of now, the cryptographic key is hard coded in the device, thus for security, this device has to be physically secure, i.e., if an adversary has access to both the encrypted memory and the MiddleMan then no security remains. This is because we have not implemented any specialized key management in the system. The design of MiddleMan allows for other modes of key inputs and we suggest various ways in which keys can be managed in the device. We plan to implement them in the near future.

#### 1.2The Organization of the Thesis

This thesis is organized into a total of eight chapters including the current chapter. Next we give a brief overview of the contents of the following chapters.

In Chapter 2 we discuss the general problem of storage encryption and tweakable enciphering schemes, which are the state of the art schemes for in-place storage encryption. In this Chapter we also present the detailed algorithm for STES [10], which is the algorithm that we selected for incorporation in the MiddleMan. The hardware design for STES is also briefly discussed in this Chapter.

In Chapter 3 we discuss the basics of the USB protocol. As this protocol forms the heart of MiddleMan, we discuss all relevant aspects which we required for the design and implementation of our device.

In Chapter 4 we give a design overview of the MiddleMan. In this chapter we carefully define the design goals of MiddleMan, and then do a systematic exploration of the design space and concretize our design decisions. Finally, we present the basic architecture of the MiddleMan. The design decisions are highly motivated by the technology we used to implement it. In this chapter we also discuss some basic implementational issues.

In Chapters 5 and 6 we provide the details of our design and implementations. In Chapter 5 we discuss in detail the design and implementation of the extension

<sup>&</sup>lt;sup>2</sup>Some operating systems like Windows, would ask to format the device as if there was no data, doing so will destroy the encrypted information

board for Spartan 3E. As discussed earlier we use the extension to implement some functionality of the USB physical layer. This chapter also discuss the details of the circuit diagram along with the specifications of the printed circuit board that we designed for the purpose.

In Chapter 6 we discuss the details of the USB protocol along with the encryption algorithm implemented in the FPGA. This chapter provides all details related to how the device and host protocols run inside the MiddleMan. In this Chapter we also provide the detailed circuit diagrams of the various units that implements the whole functionality of the MiddleMan.

In Chapter 7 we discuss some performance results for the device. We briefly discuss the various tools that were used to debug and test the device. Then, we present the performance of the device in terms of data transfer rates and FPGA utilization.

We conclude the thesis in **Chapter 8** and point out the limitations of our implementation and also discuss various ways to overcome these limitations and improve the design.

# Chapter 2

# Secure Storage of Data

In this chapter we discuss about storage encryption. The purpose of such an encryption is to protect data inside a persistent media. This data may be the target of a malicious entity accessing the device, either virtually trough malicious software or physically by stealing.

The main goal of this Chapter is to introduce tweakable enciphering schemes (TES) and to describe a specific TES called STES. For that purpose we need to fix some notations which we do in Section 2.1. Then, in Section 2.2 we discuss what storage encryption is and how we can achieve it by using TES. In Section 2.3 we provide a formal definition of TES, and also briefly mention some existing constructions. In section 2.4 we present STES, which is the scheme of choice for this work. The description of STES presented in this Chapter closely follows the original work where STES was first proposed [10]. In Section 2.5 we discuss a hardware architecture of STES which we used in our prototype.

#### 2.1 Notations

**Binary strings:** By  $\{0,1\}^*$  we denote the set of all binary strings and  $\{0,1\}^n$  denotes the set of binary strings of length n. For  $X,Y \in \{0,1\}^*$ , by X||Y we denote the concatenation of X and Y. |X| denotes the length of X in bits. bits(X,i,j) denotes the binary string formed by the substring of X extending from position i to position i. By i0 we mean a i1 bit circular left shift of i1, i.e. if i1 = 011011 then i1 i2 = 101101.

Finite fields and string representations: By  $\mathbb{F}_q$  we mean a finite field with q elements. We shall often treat n-bit binary strings as elements in  $\mathbb{F}_{2^n}$ . For such a treatment we would see a n bit string as a polynomial with coefficients in  $\{0,1\}$ , i.e. if  $A = a_{n-1}a_{n-2} \dots a_1a_0$  be a binary string then we will treat A as the polynomial  $A(x) = a_0 + a_1x + \dots + a_{n-1}x^{n-1}$ , which is of degree at most n-1. The addition of elements  $A, B \in \{0,1\}^n$  is defined as  $A \oplus B$ , where the operation  $\oplus$  denotes the bit wise xor of the strings. For defining multiplication of strings A and B we consider them as polynomials A(x), B(x) and define  $AB = A(x) \cdot B(x) \mod q(x)$  where q(x)

is an irreducible polynomial of degree n.

#### 2.2 Storage Encryption

Common storage media like hard disks, flash memories etc. are organized into sectors of equal sizes. Securing data stored inside storage systems organized into sectors is best achieved through a paradigm called "in-place encryption". This type of encryption sees data as a collection of sectors, and it does not know about the high level organization (like files and directories) of the data. The best way to achieve in-place encryption is to implement the encryption algorithm within the controller of the storage device, i.e., the encryption scheme should be a part of the storage media itself not a part of the host computing system. In an in place encryption, when the operating system writes a block, the controller encrypts the transmitted data before being stored. Similarly, for a read procedure, the requested block is decrypted inside the memory controller before being sent to the operating system. The obvious performance guarantees required for such encryption schemes is that its throughput should match the data rates of the storage device to prevent visible delays in data transfers.

The most accepted solution to achieve storage encryption is by the use of Tweakable Enciphering Schemes (TES) [20], which we discuss in the next section.

#### 2.3 Tweakable Enciphering Schemes

Let Key, Tweak, Msg be a finite non empty sets which we call as the key space, tweak space and message space respectively. A tweakable enciphering scheme is a function  $\mathcal{E}: \mathsf{Key} \times \mathsf{Tweak} \times \mathsf{Msg} \to \mathsf{Msg}$ . For  $K \in \mathsf{Key}$ ,  $T \in \mathsf{Tweak}$  and  $M \in \mathsf{Msg}$  we denote  $\mathcal{E}(K,T,M)$  by  $\mathcal{E}_K^T(M)$ . It is required that  $\mathcal{E}$  has the following properties:

- 1. For every  $K \in \mathsf{Key}$ , and every  $T \in \mathsf{Tweak}$ ,  $\mathcal{E}_K^T : \mathsf{Msg} \to \mathsf{Msg}$  is a permutation, which in turn implies that there exist an inverse function  $\mathcal{D} : \mathsf{Key} \times \mathsf{Tweak} \times \mathsf{Msg} \to \mathsf{Msg}$ , such that for every  $K \in \mathsf{Key}$ ,  $T \in \mathsf{Tweak}$  and  $M \in \mathsf{Msg}$ ,  $\mathcal{D}_K^T(\mathcal{E}_K^T(M)) = M$ .

- 2.  $\mathcal{E}$  is length preserving, i.e., for every  $K \in \mathsf{Key}, T \in \mathsf{Tweak}$  and  $M \in \mathsf{Msg}, |\mathcal{E}_K^T(M)| = |M|$ .

In addition,  $\mathcal{E}$  is required to have some security properties. In formal terms, a secure TES is supposed to be a *strong pseudo-random permutation* [28]. As we would not further require to treat TES in a formal manner thus we do not try to formally define security properties of TES here. Informally, for a secure TES, the outputs of both  $\mathcal{E}$  and  $\mathcal{D}$  should "look" like random strings to any computationally bounded adversary.

For the purpose of disk encryption the set Msg should contain equal length strings of size same as the sector size of the storage media where the algorithm needs to be applied, for current hard disks the sector sizes are 4096 bytes and for USB memories it is 512 bytes. The tweak is considered to be the sector address. The tweak provides some variability of the cipher text in the sense that if the same message is stored in two different sectors (with different sector addresses) then they get encrypted by distinct tweaks and hence the corresponding ciphertexts are different.

In the last decade there has been significant advancements in constructions of secure TES. The first complete construction of a TES to be used for disk encryption was CMC [20]. After this, several schemes appeared in the literature, and all the schemes use a block-cipher as the main cryptographic primitive. Currently available TES are classified in three main groups: encrypt-mask-encrypt, hash-counter-hash and hash-encrypt-hash. We briefly discuss these three paradigms of TES construction next:

- Encrypt-Mask-Encrypt type schemes have two layers of encryption with a lightweight masking layer in between. Examples from this class of schemes are CMC [20], EME [21] and EME\* [18].

- Hash-Counter-Hash type schemes have two layers of universal hashing with a counter mode of encryption in between. XCB [31], HCTR [37], HCH [8] and HMCH [32] are some examples of this class of schemes.

- Hash-Encrypt-Hash uses two universal hash functions along with an Electronic Code Book encryption step in between. Examples of this class of schemes are PEP [11], TET [19] and HEH [33] etc.

In terms of efficiency, to encrypt a m block message (where the block size is same as the block size of the underlying block cipher, for example, for AES the block size is 128 bits) the hash-encrypt-hash type schemes require about 2m block cipher calls. The other schemes require both block cipher calls along with finite field multiplications. HMCH and HEH require about one m block cipher calls and m finite field multiplications, all other schemes mentioned above in the hash-counter-hash and hash-encrypt-hash categories require about m block cipher calls and 2m finite field multiplications.

Recently a TES called STES was proposed in [10]. STES is different from the previous proposals by the fact that it uses stream ciphers instead of block ciphers. The main motivation behind the design of STES was to have a secure TES which when implemented in hardware would have a small hardware footprint, such that the algorithm can be used for encryption in small and power constrained devices. In [10] STES was implemented with various datapaths, and the results demonstrate that STES provide excellent time-area trade-off and when implemented in certain class of FPGAs has very low power consumption. Because of these encouraging features of TES we decided to use STES in MiddleMan. In the next section we give an overview of the construction of STES which follows closely the description in [10].

#### 2.4 STES Construction

The two main building blocks of STES are a special universal hash function called MLUH and a stream cipher.

A Stream Cipher is a function  $SC_K : \{0,1\}^{\ell} \to \{0,1\}^L$  where  $\ell \ll L$ . This function takes as input an initialization vector (IV) of small length  $\ell$  and outputs a long and random looking string L.

STES construction also uses a particular hash function called Multilinear Universal Hash. A multilinear hash function with output length b and datapath d is defined as

$$\mathsf{MLUH}^{d,b}_K(M) = h_1||h_2||\cdots||h_b$$

where the input message M is written as  $M = M_1 || M_2 || \cdots || M_m$ , the key K is written as  $K = K_1 || K_2 || \cdots || K_{m+b-1}$ , such that  $|M_i| = d$  for  $1 \le i \le m$  and  $|K_i| = d$  for  $1 \le i \le m+b-1$ , and

$$\begin{array}{rcl}

h_1 & = & M_1 \cdot K_1 \oplus M_2 \cdot K_2 \oplus \ldots \oplus M_m \cdot K_m \\

h_2 & = & M_1 \cdot K_2 \oplus M_2 \cdot K_3 \oplus \ldots \oplus M_m \cdot K_{m+1} \\

\vdots & \vdots & \ddots & \vdots \\

h_b & = & M_1 \cdot K_b \oplus M_2 \cdot K_{b+1} \oplus \ldots \oplus M_m \cdot K_{b+m-1}.

\end{array}$$

(2.1)

The additions and multiplications in the above equations are in  $\mathbb{F}_{2^d}$ .

STES uses a stream cipher with IV SC, and a multilinear hash function as shown in Figure 2.1. The algorithm also makes calls to an external function called Feistel which is shown in Figure 2.2.

The algorithm is parameterized on the key K and tweak T, additionally it uses a string fStr. It has been mentioned in [10] that the string fStr can be a public constant. The algorithm assumes that the length of the IV of the stream cipher used is  $\ell$  bits and the datapath of the MLUH (described in Eq. 2.1) is d.

### 2.5 Implementation of STES

In this work we did not implement the STES, but used an implementation done by Cuauhtemoc Mancillas-López. We only adapted the implementation for its proper use within the MiddleMan. For completeness we describe briefly the architecture of STES that we used, the description again is adopted from the original article [10].

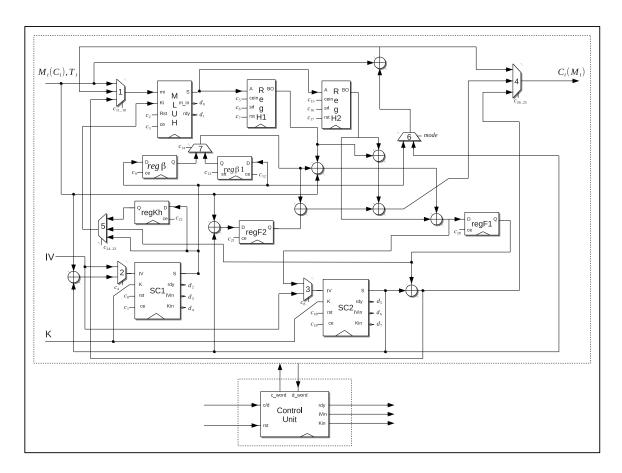

For our implementation we instantiated the stream cipher using Trivium, which uses a 80 bit IV, and we used a MLUH with 8-bit data path. The architectural overview is shown in Figure 2.3. Next we describe the architecture with reference to the algorithm in Figure 2.1.

The circuit presented in Figure 2.3 consists of the following basic elements:

1. The MLUH constructed with 8-bit multipliers.

Figure 2.1: STES: A TES using SC and MLUH. The  $\ell$ -bit string fStr is a parameter to the whole construction. The length of the IV of SC is  $\ell$  and the data path of MLUH is d. This figure has been taken verbatim from [10].

```

\mathsf{Feistel}_{K,\tau''}^{\ell,d}(A_1,A_2,i)

InvFeistel_{K,\tau''}^{\ell,d}(B_1,B_2,i)

1. H_1 \leftarrow \mathsf{MLUH}^{d,b}_{\tau''}(A_1);

1. H_2 = \mathsf{MLUH}_{\tau''}^{d,b}(B_2);

2. F_1 \leftarrow H_1 \oplus A_2;

2. F_2 = H_2 \oplus B_1;

3. (G_1, W) \leftarrow \mathsf{SC}_K^{\ell+i}(F_1);

3. G_2 = SC_K^{\ell}(F_2);

4. F_1 = B_1 \oplus G_2;

4. F_2 \leftarrow A_1 \oplus G_1;

5. (G_1, W) = \mathsf{SC}_K^{\ell+i}(F_1);

5. G_2 \leftarrow \mathsf{SC}_K^{\ell}(F_2);

6. B_2 \leftarrow F_1 \oplus G_2;

6. A_1 = F_2 \oplus G_1;

7. H_2 \leftarrow \mathsf{MLUH}^{d,b}_{\tau''}(B_2);

7. H_1 = \mathsf{MLUH}_{\tau''}^{d,b}(A_1);

8. B_1 \leftarrow H_2 \oplus F_2;

8. A_2 \leftarrow H_1 \oplus F_1;

return(B_1, B_2, W);

return(A_1, A_2, W);

```

Figure 2.2: The Feistel network (and its inverse) constructed using a stream cipher and a MLUH. The variable  $\ell$  is the length of an IV for SC and d is the data path of MLUH. This definition is different from the usual Feistel construction: a positive integer i is provided as an additional input and a binary string W of length i is returned as an additional output. This figure has been taken verbatim from [10].

- 2. Two stream cipher cores labeled **SC1** and **SC2**.

- 3. Two 80-bit registers **RegH1** and **RegH2** which are used to store the output of **MLUH**.

- 4. Four registers labeled regF1, regF2, regKh and  $reg\beta$ . All these registers are 80 bits long and are formed by ten registers each of eight bits connected in cascade, so that they can be used as a FIFO queue.

- 5. One special register  $reg\beta 1$  which is able to store a 80-bit data and rotate it in one bit position. This register outputs 8-bit data each clock cycle when the control input ce is activated.

- 6. Seven multiplexers labeled 1, 2, 3, 4, 5, 6 and 7.

- 7. The control unit whose details are not shown in the Figure.

- 8. The connections between MLUH and the registers RegH1, RegH2 have a data path of 80 bits. All other connections have a data path of 8 bits.

- 9. The input lines  $M_i$ , IV and K which receives the data and tweak, the initialization vector and the key respectively.

- 10. The output line  $C_i$  which outputs the cipher.

The **MLUH** computes the MLUH, it receives as inputs message blocks  $M_i$ , tweak blocks  $T_i$  and key blocks  $K_i$  and give as output the result of MLUH in its output port S. The register **RegH1** and **RegH2** receive the output from S as input, in this case |S| = 80 bits. The registers **RegH1** and **RegH2** are designed to give eight bit

Figure 2.3: Architecture of STES

blocks as outputs in each clock cycle in their output port BO. The **MLUH** receives its input from the  $3 \times 1$  multiplexer labeled **1**. Notice, that in the algorithm of STES, the MLUH is called on three different inputs. Multiplexer **1** helps in selecting these inputs. In the algorithm MLUH is called on two different keys  $\tau'$  and  $\tau''$ , thus, **MLUH** can receive the key from two different sources: the key  $\tau'$  is received directly from the output of the stream cipher **SC1** or **SC2**. The key  $\tau''$  is received either directly from stream cipher **SC1** or from the register **regKh** which is used to store  $\tau''$ . To accommodate these selection of keys the input port Ki of **MLUH** receives the input from the  $2 \times 1$  multiplexer **5**.

We use two stream ciphers **SC1** and **SC2**. Both take the key from the input line K of the circuit. **SC1** receives the IV from multiplexer **2**, it selects between input line IV or  $F_1$ . Multiplexer **3** feeds the IV to the stream cipher **SC2**, it selects between IV or  $F_2$ .

In the algorithm of STES we can see that the output of MLUH is xored with the value of  $\beta$ , or  $\beta \ll 1$ , depending which hash is computed  $Z_1$  or  $Z_2$  and whether encryption or decryption mode is being executing. The selection between these two values is made with Multiplexer 7.

In the encryption mode the stream W is generated using SC2 but in the decryption mode it is generated by SC1. Multiplexer 6 is used to select the correct stream cipher to produce the cipher text or plain text.

# Chapter 3

## The Universal Serial Bus

The Universal Serial Bus (USB) is a popular interface, which has been in use for several years. Almost all computer devices use this interface to provide various functionalities, ranging from basic I/O to video and audio devices.

In this chapter we provide general information on the most important aspects of the USB interface. We begin with an introduction to the bus in Section 3.1, this is important to understand the bus interconnection. Then, we discuss the internal USB components. In Section 3.2 we give a short introduction to the Physical Layer (PHY), in Section 3.3 we discuss about the Serial Interface Engine (SIE) and in Section 3.4 we discuss the USB Endpoints (ENP). These components are the building blocks for every USB device.

Section 3.5 introduces the transactions, which are the lowest level protocol of the USB communication. We also present the packet structure in this section. Transfers are build upon transactions, we discuss about the transfer types in Section 3.6.

Some tables and figures, which we used to explain several parts of the protocol, where partially taken from the USB specification [12] or the book by Axelson [6]. The description of the bus and its functionality that we provide here is not detailed, the reader may consult [12, 6] for more detailed information on the USB specification.

#### 3.1 USB Basics

In this section we discuss about the basics of the USB specification. We begin by defining the bus entities and its topology in Section 3.1.1. Then we present the four speeds available in Section 3.1.2.

#### 3.1.1 Components of the bus

USB is an interface created to achieve communications between a host entity and several devices. The purpose of this communication is to provide extra functionality to the host, which can be a computer or an embedded system.

Several entities can interact in the bus at the same time. We list some of these entities along with their basic functionality next:

- **Host**: Master and manager of the bus, it detects newly attached devices and configures them in order to begin communication. It schedules bus time for each of the devices attached to the bus.

- **Device**: This entity provides some functionality to the host. The most common functionality is the external data storage.

- Hub: The Hub routes communications between the Host and any other Hub or device attached to it's ports. It also manages bus speed conversion (low speed devices connected to a high speed bus). The Hub can have multiple ports where Devices or other Hubs can be attached. The host connects directly to a Hub called the "Root Hub".

- Compound device: this device is a combination of a Hub and a Device in a single entity.

The bus topology is a tiered star as shown in Figure 3.1. In this topology, each hub is a star center. Tiers are added by connecting additional Hubs in series, up to five tiers can be attached with a total number of 127 devices (including the root Hub). Despite the limit in the number of devices, it is impractical to have this many devices attached to the bus at the same time. The host assigns bus time based on the number of devices connected to the bus. Too many devices means less bus time for each of them.

Figure 3.1: USB topology

Inside each entity there are three basic components, the Physical Layer (PHY), the Serial Interface Engine (SIE) and the Endpoint (ENP), their relationship is shown in Figure 3.2. The endpoint section is only available for Hubs and Devices.

Figure 3.2: USB device components

#### 3.1.2USB Supported Speeds

The USB specification defines four speed configurations, these are shown in Table 3.1. The host detects the speed of a device by checking the D- and D+ lines shown in Figure 3.2. If a device has the D-line connected to 5V through a resistor, the host detects it as a low speed device. Full speed is detected if the device has D+ connected to 5V through a resistor instead. Every high speed device connects to the USB bus at full speed. When the host requests a device to enable high speed, if this device supports it, then it will respond to this request and the host enables high speed.

| Speed       | Data rate | Common applications   | Supported USB versions |

|-------------|-----------|-----------------------|------------------------|

| Low speed   | 1.5 Mbps  | input peripherals     | 3.0 and below          |

| Full speed  | 12 Mbps   | Data transfer         | 3.0 and below          |

| High speed  | 480 Mbps  | Data, Audio and Video | 3.0,2.0                |

| Super speed | 5 Gbps    | Data transfer         | 3.0                    |

Table 3.1: USB speed configurations

The host requests high speed by using a protocol called "Chirp Protocol", it uses the signaling that will be explained in Section 3.2. The Chirp Protocol follows a sequence of K and J USB bus states, which we define in Table 3.2. We explain the basic steps next:

- 1. The host detects a full speed device, then it resets the bus.

- 2. The device responds to the reset by transmitting a full speed K state for no less than 1ms.

- 3. When the host detects the K state for at least  $2.5\mu s$ , it waits for the device to stop transmission. After this, the host transmits a series of K and J states.

4. The device must detect the state sequence K-J-K-J. Each state must last  $2.5\mu$ s. After the sequence has been detected, the device enables high speed.

USB 3.0 and super speed are not covered in this work, refer to [6] for more information on these standards.

### 3.2 The Physical Layer

The Physical Layer (PHY) is the component which deals with the physical connection in the USB bus. The responsibilities of this component are to detect the start and end of a packet in order to receive it properly. This component also decodes or encodes data transmitted from/to the bus. Encoding is explained later in this section.

The USB bus uses differential signaling techniques in order to transfer data. A differential signal is transmitted over a pair of wires which have opposite voltage levels, the USB naming convention for this pair of wires is D+ and D-. Table 3.2 shows the signal levels and possible bus states.

| Bus state            | Signal level                           |

|----------------------|----------------------------------------|

| Differential 1       | D + = high, D - = low                  |

| Differential 0       | D + = low, D - = high                  |

| Single ended 0 (SE0) | D + = low, D - = low                   |

| Single ended 1 (SE1) | D + = high, D - = high                 |

| J state:             |                                        |

| Low speed            | Differential 0                         |

| Full speed           | Differential 1                         |

| High speed           | High speed differential 1 <sup>1</sup> |

| K state:             |                                        |

| Low speed            | Differential 1                         |

| Full speed           | Differential 0                         |

| High speed           | High speed differential 0 <sup>1</sup> |

Table 3.2: USB 2.0 signaling

There are two types of PHYs defined by the USB specification: upstream and downstream. We will explained them next:

- A downstream facing PHY goes from a Host or Hub to a device. It has two resistors connected to ground on D+ and D- lines.

- An upstream facing PHY goes from a device to a Hub or Host. This PHY has a resistor on D- connected to 5V for low speed, for full speed, the resistor is connected from 5V to D+ instead.

<sup>&</sup>lt;sup>1</sup>Full and high speeds differ in voltage levels, refer to USB 2.0 [12, pp. 145-147]

The USB specification requires the codification of bus data in the format called "non-return zero invert format" (NRZI). NRZI represents data by a level change instead of a logic level. In NRZI, a logic '0' is represented by a state change, a logic '1' is represented by not changing the previous state; Figure 3.3 shows a codification example. This codification must also stuff bits inside the data as follows: When there are six consecutive '1', the PHY must stuff a '0' before encoding, this guarantees regular changes in the bus state. Regular changes are needed by the PHY to keep synchronization of bus data.

Figure 3.3: NRZI encoding

#### 3.3 Serial Interface Engine

The Serial Interface Engine (SIE) has several functions inside a USB host or device entity. These functions are summarized next:

- Data conversion: The SIE receives data in serial format and converts it to parallel. It also converts transmitted data from parallel to serial.

- Error checking: The SIE performs error checking of the received data by calculating a Cyclic Redundancy Code (CRC). This code is compared against a CRC appended at the end of each received USB packet. The packet is discarded if the codes differ. CRC calculation procedure for USB packets is described in Appendix A.2.

- Acknowledge successful transmissions: The SIE must send an acknowledge (ACK) packet for every data packet received without errors, this process is called "Handshake".

#### 3.4**Endpoints**

The endpoint (ENP) is the main source and sink of data. In order to communicate with a device, a host controller addresses a specific endpoint inside a device. Endpoints can have two directions:

• IN endpoints store data to be sent to the host.

• **OUT** endpoints receive data from the host.

Full and high speed devices can have up to 32 endpoints (16 IN and 16 OUT). Every device must implement at least the default endpoint, which consists of the endpoint 0 in both directions. Configuration of any USB device is done through the default endpoint using a transfer type called "control transfer". We discuss this transfer type in Section 3.6. In addition to control transfers, Endpoints can be configured to respond to other types of transfers, which are also discussed in Section 3.6.

#### 3.5 Protocol

This section describes the basics of the USB protocol. There are several concepts behind low level USB communication, which we present in this section. We discuss transactions and packet structures in Sections 3.5.1 and 3.5.2, these are the building blocks for USB transfers, which we introduce USB transfers in Section 3.6.

#### 3.5.1 Transactions

Transactions are the lowest USB communication protocol. They are performed in the following sequence:

- 1. The host sends a token packet to the device

- 2. If the token is an OUT token, then the host send data. If the token is an IN token, then the device sends data.

- 3. The receiver of the data in the last step responds with an acknowledge packet. Only error free packets are acknowledged.

The host divides the bus time in intervals of 1ms called "Frames". during each frame, the host and device can exchange data. For high speed, the host divides each frame in eight parts of 125  $\mu$ s. These parts are called "Micro frames". The host signals the start of each frame by sending a special token called Start of Frame (SOF). The device may use this packet to detect bus activity. If the host stops sending SOFs for more than 3 ms, the device must enter into a suspend mode, which consumes less power.

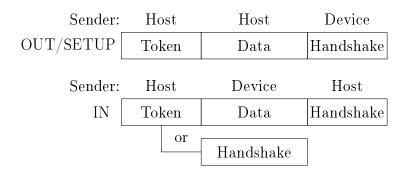

The structure of a transaction is shown in Figure 3.4. Transaction type is sent by the host in the token stage, there are three types of transactions:

- IN: Data travels from the device to the host. If the device has no data to send, then it responds with a handshake (acknowledge) packet.

- **OUT**: Data travels from the host to the device.

- **SETUP**: Data travels from the host to the device. This token is used to indicate that the data contains a command for device configuration.

Figure 3.4: Stages of a transaction

#### 3.5.2Packet Structure